NVMe 1.2 Redefines SSD Design As Marvell Releases HMB SSD Controller

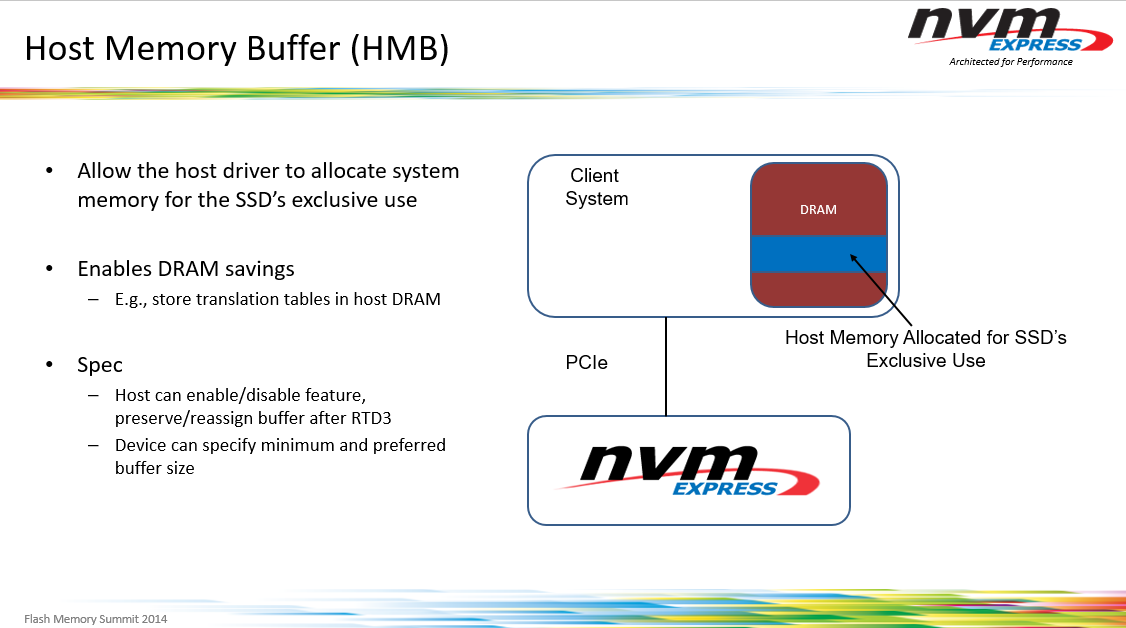

Marvell released its 88NV1140 SSD controller at CES 2016 in a move that will likely lead to a sweeping change in the way manufacturers design SSDs. The new controller utilizes the new HMB (Host Memory Buffer) feature in the NVMe 1.2 protocol, which allows an SSD to utilize system RAM for its own purposes. The HMB functionality is baked into the open source NVMe protocol, so we should expect similar support from a number of other SSD controller manufacturers as the industry continues its inexorable push to lower SSD prices and increase density.

It is not a secret that the price of SSDs is plummeting quickly. A few short years ago, we dreamed of the day when an SSD would be only $1-per-GB, which pundits held forth as the inflection point for mainstream adoption. The $1-per-GB psychological price barrier was broken, and in ensuing years, we have witnessed prices plunge to 35-cents-per-GB.

NAND is easily the most expensive component on an SSD; it comprises roughly 80 to 95 percent of the BOM (Build Of Materials) cost, depending upon the SSD architecture. The best way to reduce cost, outside of relying upon the naturally decreasing cost of the NAND, is to remove some of the other components onboard the SSD. The first item to go is the DRAM, which is expensive in comparison to NAND.

Chris Ramseyer, our storage editor, pointed out this emerging trend at Computex 2015 in his The Race To The Bottom Travels Without DRAM: Low Cost SSDs article. As Chris noted, one of the drawbacks to removing DRAM from the design is that it reduces performance significantly. Contrary to popular belief, the SSDs' DRAM is rarely used for caching user data, largely due to data safety concerns.

Instead, SSD vendors employ the DRAM buffer to hold the translation tables (which at its most basic level is a map of the abstracted addresses of the data stored on the NAND). Utilizing speedy DRAM to "look up" the location of the data speeds overall SSD performance. Hosting the LBA tables on the NAND, the current method in DRAM-less SSDs, slows this process (and thus overall performance) tremendously.

The NVMe consortium designed the ever-evolving NVMe specification to offer a lightweight software stack to all non-volatile memories, not specifically NAND. This means the interface is efficient enough to even handle the speeds of DRAM (and beyond), so adding the ability to manage a portion of the system memory (RAM) for the SSD easily falls into the realm of the possible. Allowing the SSD controller to control an adjustable portion of the host memory keeps performance high, but it also keeps cost low for the SSD vendor.

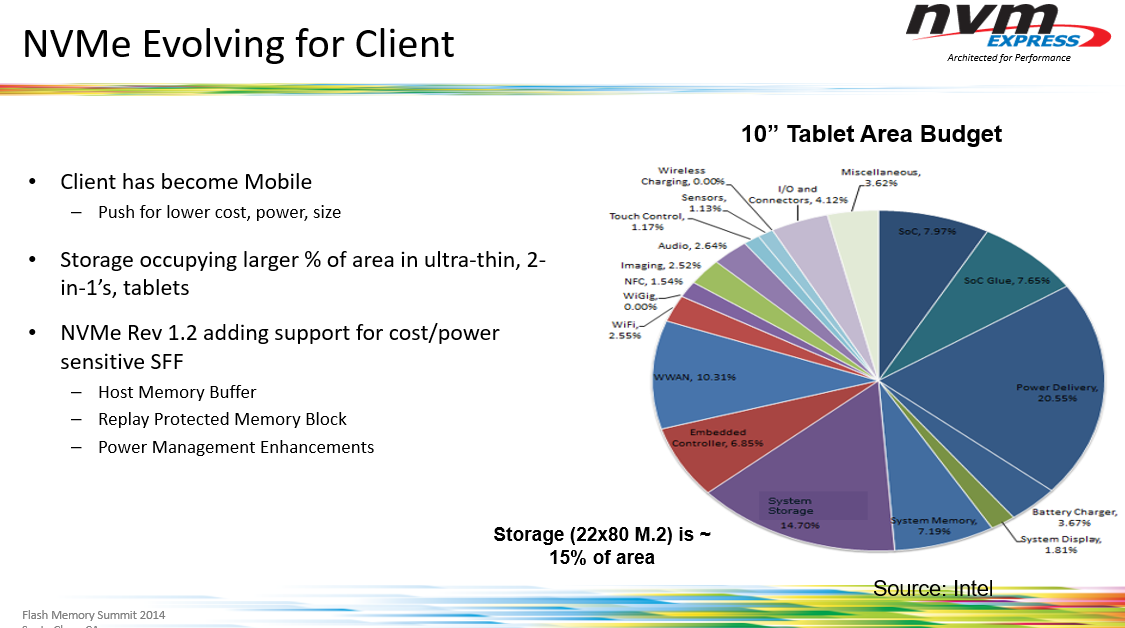

The need to miniaturize components is a never-ending endeavor in space-constrained mobile environments, and storage is no exception. Currently, in a 10" tablet, the storage solution requires a minimum of 15 percent of the overall area inside the device. As other components continue to shrink, such as batteries, the storage consumes a higher percentage of the space inside the device. The nature of NAND density improvements, which occur with each successive generation, help address the need to consume less real estate, but removing the dedicated NAND package is a huge step forward. It also reduces power consumption, which is always a welcome addition in mobile environments.

Stay On the Cutting Edge: Get the Tom's Hardware Newsletter

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Storing the translation tables in the DRAM raises concerns; the tables can be lost during an unsafe power loss. Most mobile devices are battery powered, so the majority of unsafe power loss events will likely occur from BSOD issues. The NVMe spec allows manufacturers to checkpoint (copy at regular intervals) the data in the DRAM to the NAND, to reduce (but not remove entirely) the possibility of data loss due to power failures.

HMB designs will likely emerge on controllers designed specifically for mobile and embedded applications, such as Marvell's new 88NV1140 SSD controller. Marvell indicated that the 88NV1140 offers performance within close range of a normal DRAM-infused SSD, and it supports all of the latest bells and whistles we expect with a leading-edge SSD controller.

Marvell's NANDEdge LDPC algorithms allow vendors to extract the maximum possible endurance from TLC (including 15nm) and 3D NAND, which is another key factor to reducing cost. Utilizing large amounts of DRAM to mask the performance loss often associated with TLC-based SSDs is a perfect tandem. The controller also supports 3D NAND and wields a dual-core Cortex R5 processor.

The controller employs onboard SRAM, another common addition in DRAM-less SSDs, with hardware accelerators to boost performance. Marvell built the controller upon its low-power 28nm process, which also supports the new L1.2 power management features added in NVMe 1.2. The newest revision of the spec features an enhanced thermal throttling technique for client SSDs, which is important in dense mobile designs and a wide range of enterprise enhancements.

Marvell indicated that it is working with leaders in the PC segment to foster broader support for HMB, and we expect OEMs to embrace the new technology quickly due to its obvious benefits.

One of the interesting caveats is that the SATA protocol provided host-offload of the NCQ queue a few years ago, but the offload efforts never progressed to more enhanced techniques, such as the NVMe-powered HMB tactic. NVMe continues to become more attractive than SATA due to its forward-thinking design and improved functionality, and the specification will continue to supplant SATA devices in mobile devices in the months to come.

1-11-16 15:08 CT - Corrected article title to "HMB".

Paul Alcorn is the Managing Editor: News and Emerging Tech for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

nitrium Headline has HBM (aka High Bandwidth Memory), but article only talks about HMB (Host Memory Buffer).Reply

"NVMe 1.2 Redefines SSD Design As Marvell Releases HBM SSD Controller". -

PaulyAlcorn Thanks nitrium, article title corrected.Reply

Too bad it isn't an HBM controller for an SSD though, now that would be saucy. :ouch: -

alextheblue Great let's chew up system RAM for the sake of cheaper SSDs. Now slap it in a pile of cheap OEM 2-in-1s with not-quite-enough slow-as-dirt single-channel memory and an iGPU to share it all with. Awesome. Here's hoping 8GB of DDR4 becomes the new baseline in the near future.Reply

Still, I guess it beats what they normally do, which is stuff a mechanical drive in them and laugh maniacally. -

Sakkura After the last image:Reply

"The nature of NAND density improvements, which occur with each successive generation, help address the need to consume less real estate, but removing the dedicated NAND package is a huge step forward."

I think you mean removing the dedicated DRAM package. -

DrakeFS ReplyGreat let's chew up system RAM for the sake of cheaper SSDs. Now slap it in a pile of cheap OEM 2-in-1s with not-quite-enough slow-as-dirt single-channel memory and an iGPU to share it all with. Awesome. Here's hoping 8GB of DDR4 becomes the new baseline in the near future.

Still, I guess it beats what they normally do, which is stuff a mechanical drive in them and laugh maniacally.

I haven't built or bought a system with less than 8GB of ram in a long time. And if you are purchasing cheap OEM systems, lets be honest, performance is not your main concern. -

ssdpro I'm with Alex the blue. I want my data in non-volatile storage as quickly as possible. We already have file system caching. Now to increase profit on the mfg side they skimp on the internal DRAM and hold it in memory longer. I want a one stop solution, not a cobbled janky piecemeal gadget.Reply