Apple, Intel Could Become First to Adopt TSMC's 2nm Node

Intel expected to become another alpha customer of TSMC.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Taiwan Semiconductor Manufacturing Corp. is set to start high volume production of chips using its N2 (2 nm-class) process technology in late 2025 and deliver the first batch of these chips in early 2026. According to two media reports and sources within the financial community, the first customers to adopt N2 will be Apple and Intel.

Apple and Intel First to Use TSMC's N2

Apple has been TSMC's largest customer by revenue contribution for about a decade, so it is not surprising that it will also be an alpha customer for N2. As for Intel, the company intends to use TSMC's services to make graphics processing units (GPUs) and various SoCs, two types of applications that benefit from leading-edge nodes. So, it is not surprising that Intel will also be one of the early adopters of N2, according to reports by DigiTimes and UDN. Furthermore, given Intel's volumes, it will quickly become one of the foundry's primary customers.

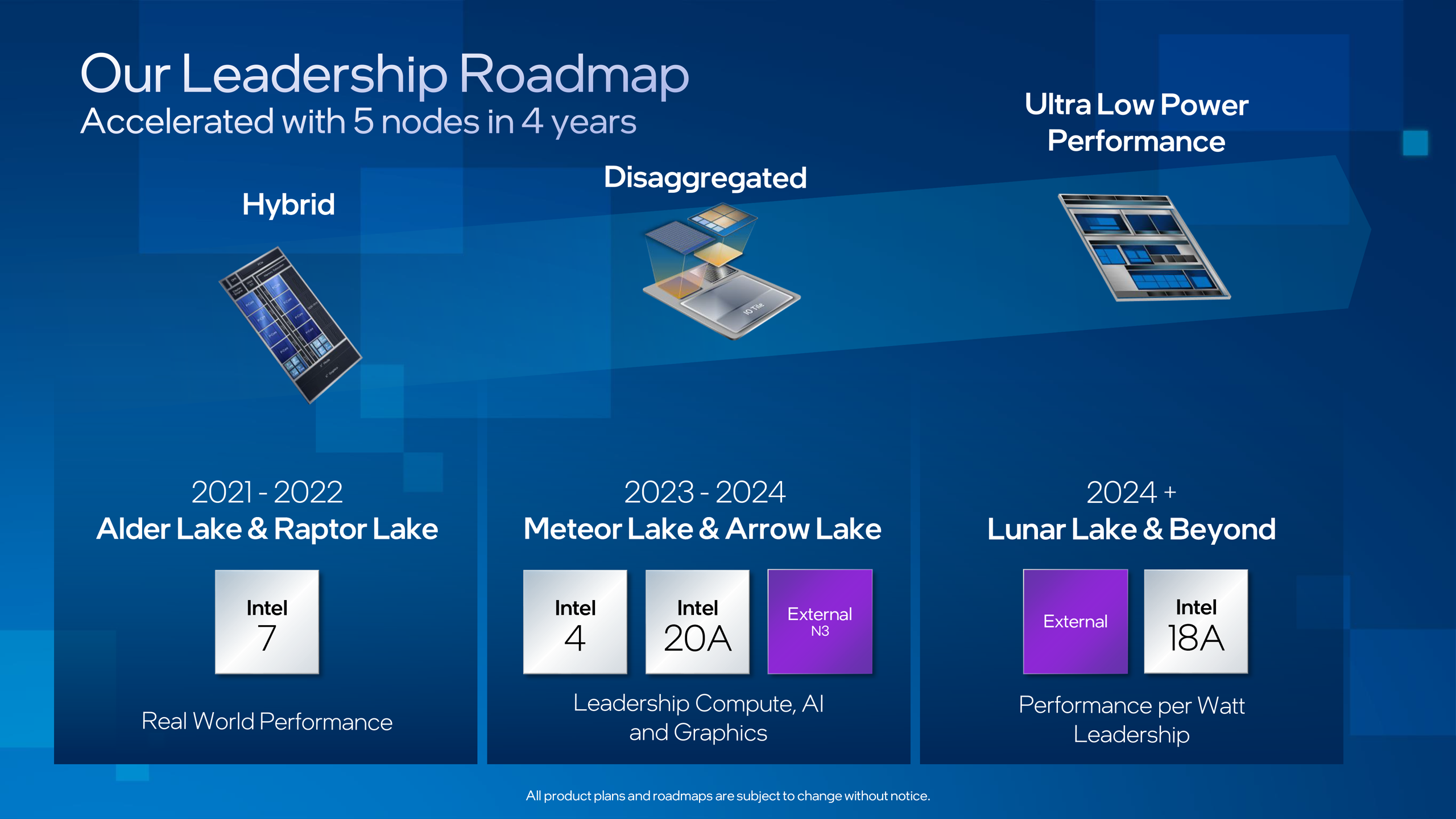

Since the first batch of N2 chips should be delivered in early 2026, it is unclear which of Apple's system-on-chips (SoCs) will use it then. Meanwhile, analysts from China Renaissance Securities speculate that Intel will use TSMC's N2 for the graphics tile in its codenamed Lunar Lake processor.

Article continues below"We also see more clarity around TSMC's N2 expansion schedule in Fab 20 (Hsinchu)," Sze Ho Ng, an analyst with China Renaissance Securities, wrote in a note for clients. "Tool move-in is expected to start by end-2022, based on company plans, ahead of risk production in late 2024E with Intel (client PC Lunar Lake's graphic 'tiles', while the CPU 'tiles' are fabbed using Intel’s 18A) and Apple being the anchor customers for dedicated capacity support."

The usage scenario of N2 for Lunar Lake is speculation at this point. However, Intel's own slide that describes graphics tiles of Meteor Lake, Arrow Lake, and Lunar Lake processors clearly indicates that the latter's GPU will be made externally using a technology that is more advanced than N3.

AMD, Nvidia, MediaTek to Use N3, N2

AMD, Broadcom, Nvidia, and MediaTek have formally confirmed that they will use various nodes from TSMC's N5 family (N5, N5P, N4, N4P, N4X). MediaTek has already formally introduced its N5-based Dimensity 8000/8100 application processors and N4-based Dimensity 9000 SoC, whereas Nvidia will use a custom 4N fabrication process for its Hopper and presumably Ada Lovelace GPUs. AMD's Genoa and Raphael processors will also be made using a 5 nm technology.

According to the DigiTimes report, all of these companies are currently in talks with TSMC over allocation for N3-capable capacities starting late 2023 or sometime in 2024. In addition, these companies are also expected to start talks regarding N2-capable allocations next year, though they will certainly adopt N2 significantly later than Apple and Intel.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

N2: Coming in 2026

TSMC's N2 will be the foundry's first technology to adopt gate-all-around field-effect transistors (GAAFET), years after Samsung's 3GAE (2023) and over a year after Intel 20A (2024). So far, the world's largest contract maker of chips has not disclosed what to expect from N2 in terms of power, performance, and area/transistor density improvements over N3. However, considering the fact that this will be a brand-new node, it is reasonable to expect tangible advantages over its predecessors. The new fabrication process will continue to rely on proven extreme ultraviolet (EUV) lithography scanners with a 0.33 numerical aperture. By contrast, Intel's 18A is set to use innovative ASML's Twinscan EXE EUV scanners with High-NA (0.55NA).

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

maik80 Reply

Apple has been doing this for a long time, but as it is responsible for TSMC being where it is ispeachpuff said:Is intel in a way sabotaging others by hogging the latest process from tsmc?

more than fair -

JayNor Raja has apparently been given the green light to reserve capacity far in advance. For Ponte Vecchio, CEO Bob apparently allowed the same thing, since Intel used the TSM N5 for its compute tiles. Now that the ARC GPUs are on TSM N6, it makes sense for the Meteor Lake ARC tile to be on a TSM process.Reply -

escksu Replypeachpuff said:Is intel in a way sabotaging others by hogging the latest process from tsmc?

Hog?? Intel is paying tsmc though... Its not like they are getting it free... And the latest are usually the most expensive as well. -

KyaraM Reply

Yeah, well, not that some people understand that in their blind hatred. Or that the industry is interconnected, and being able to produce one thing does not necessarily mean that you can automatically produce something else, or that you automatically have the necessary capacities to do so, or that one product can be used for different things. It all costs time and money, and it's a codependency all around. If anything, it shows that Intel wants to drastically improve products, but can't on their own (yet). So if you can't do something yourself, what do you do? Turn to the people who can.escksu said:Hog?? Intel is paying tsmc though... Its not like they are getting it free... And the latest are usually the most expensive as well.

It's so ironic. People bash Intel all the time telling then to get their stuff in order, but when they do, it's bad, too, and now they are "hogging resources". They want Intel to sell cheap, powerful CPUs, but they also have to produce them completely themselves, no help allowed. Doesn't matter how much that costs, they should just make a loss on it for everyone, and when they do and AMD, who are allowed to outsource everything, don't, more bashing and gloating on top of potential stakeholder lawsuits and stuff like that. Decide on one thing, guys. And get a basic grip on economy. Btw, this article makes it sound as if AMD didn't even start talks yet. They either need to get up earlier, or don't have a use for the node yet. Either way, it's their own fault. And it's on TSMC to gauge interest and expand accordingly. -

DavidC1 According to the latest information, TSMC is going into production in late 2025, meaning products in 2026. Arrowlake is 2024, which means Lunarlake is probably 2025.Reply

The chances of Lunarlake having TSMC 2nm for GPU tile is not very high. TSMC is having a bit of trouble with the plain vanilla 3nm, but much better on the variants. I'd bet on Intel using TSMC 3E. -

DavidC1 Replygg83 said:Why do GPU's in particular benefit from leading edge nodes? My than a cpu can?

They benefit equally. They are both compute intensive so die sizes can get quite large. Newer processes allow smaller dies and/or more transistors.

Newer processes also increase performance and performance per/watt which both CPUs and GPUs require.

Actually I believe by the time Lunar Lake is out, the compute(CPU) tile will be on a more advanced process than the GPU. Compute tile on Intel 18A and GPU tile on TSMC 3nm variant. -

escksu Replygg83 said:Why do GPU's in particular benefit from leading edge nodes? My than a cpu can?

Yes, gpus do benefit alot more compared to cpu. The main reason is its design. Look at cpu and see how much of the space is taken up by cache memory instead of core logic? Now look at gpu and the space used for cache, its alot smaller.

Today, the main problem is core isnt about potential performance anymore, its about efficiency. Engineers could easily add more decoder, more interger and fpu etc into a core, but performance is not going to improve. The issue is with keeping those integer and fpu busy... Thats why so much die space is allocated to cache instead of core logic -

escksu ReplyDavidC1 said:They benefit equally. They are both compute intensive so die sizes can get quite large. Newer processes allow smaller dies and/or more transistors.

Newer processes also increase performance and performance per/watt which both CPUs and GPUs require.

Actually I believe by the time Lunar Lake is out, the compute(CPU) tile will be on a more advanced process than the GPU. Compute tile on Intel 18A and GPU tile on TSMC 3nm variant.

CPUs no longer benefit as much compared to gpu is a die shrink. This is due to cpu design which most of the space is taken up by cache instead of core logic.