Inside Intel's CPU Packaging Factory: From Wafer to Chip

Touring Intel's Malaysian facilities.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

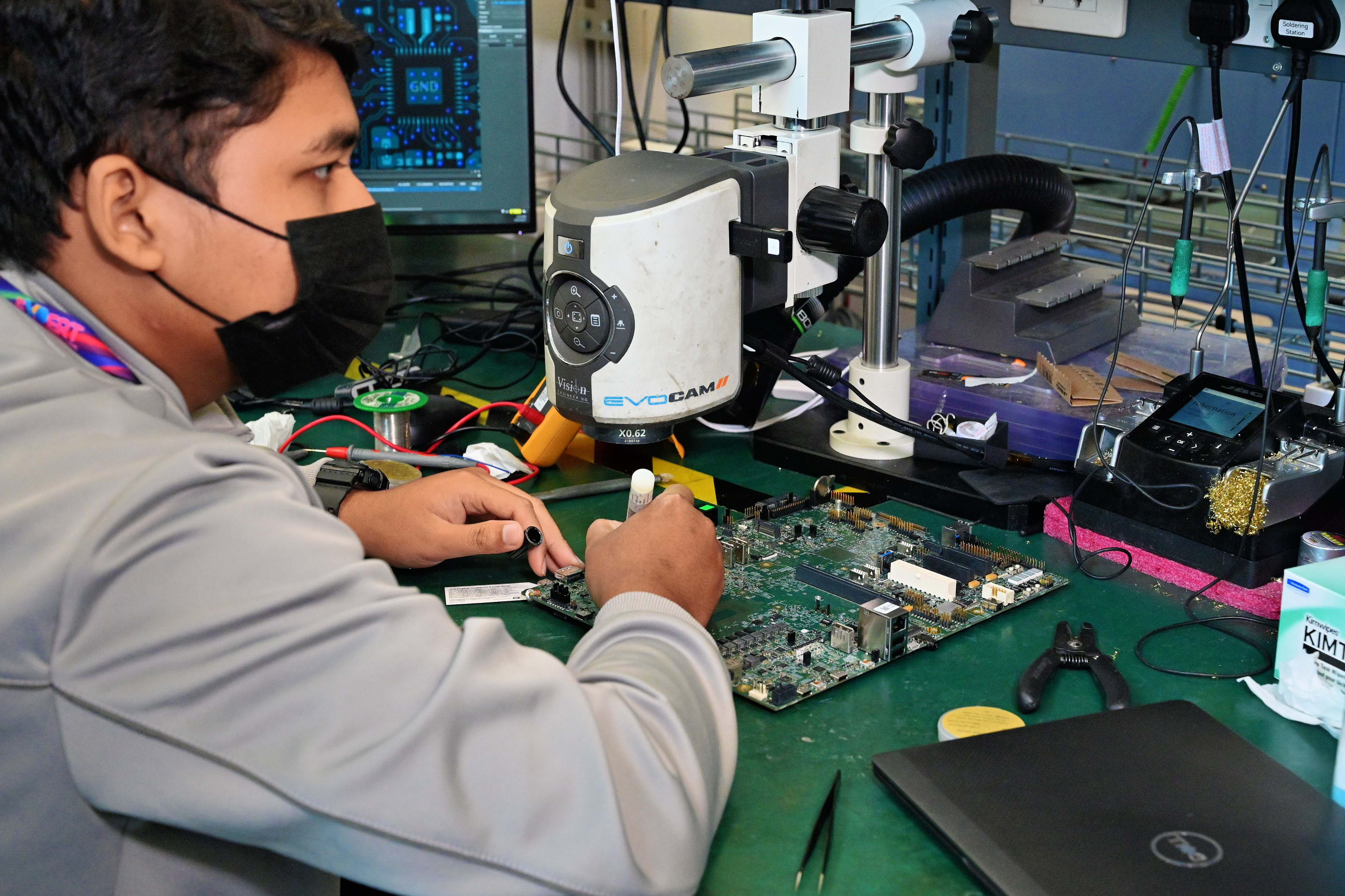

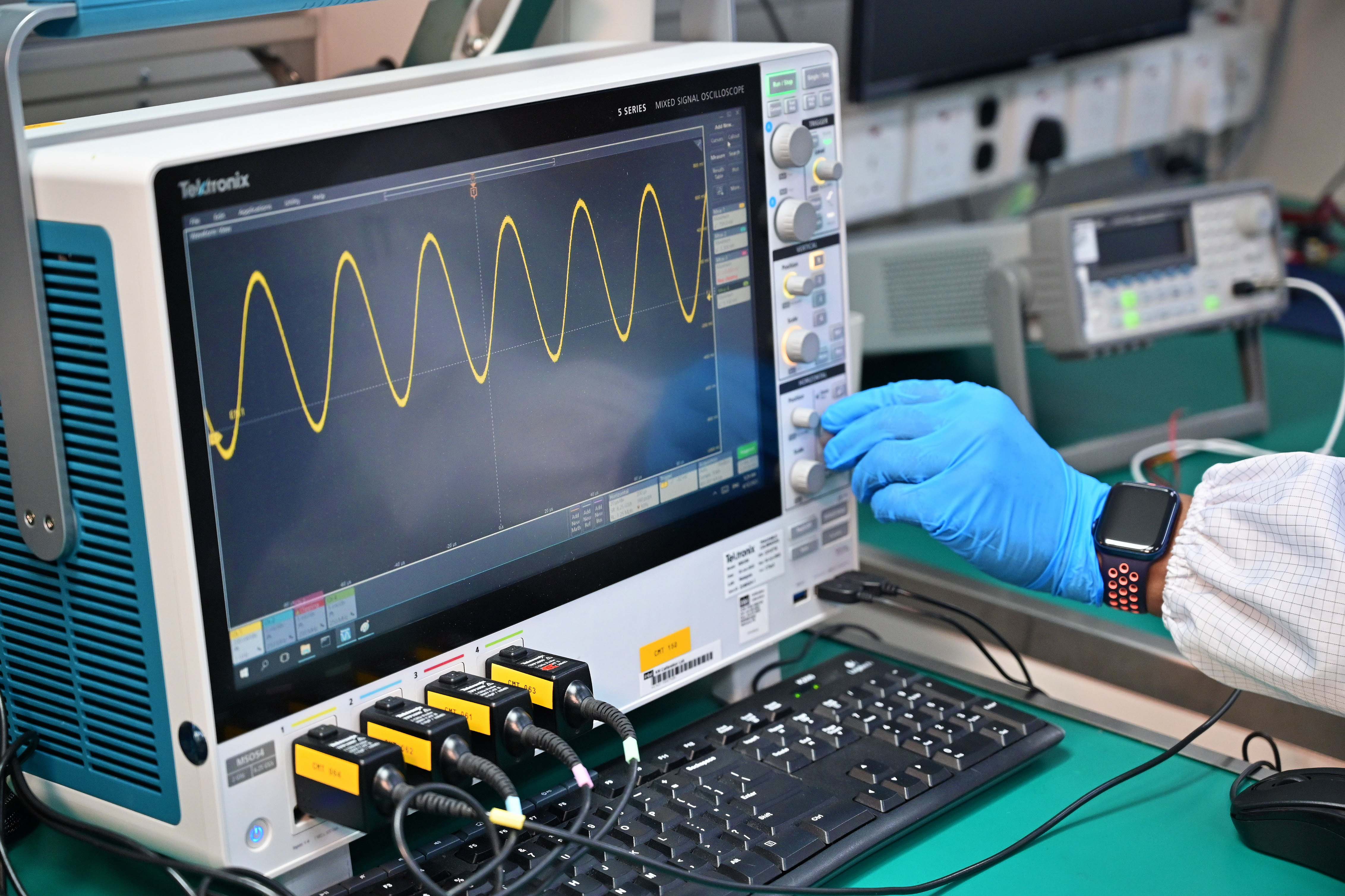

Failure Analysis Lab

Every die wants to live, but some don't. Those defective chips end up in the failure analysis lab for a series of tests to determine the nature of the fault and then, if needed, a series of deeper tests that can be destructive.

The above video shows a neat representation of one type of failure that can be seen during a 3DMark test. This demonstration shows two chips running the same sequence, with the defective chip running the program on the top monitor and the fully functioning chip running on the monitor below. During the first few seconds of the video, you can see a series of artifacts that manifest as bright lights at the bottom right of the monitor on the defective chip, and that's indicative of an error in the chip.

This chip had passed many layers of testing throughout the manufacturing process, but the defect was found during the PPV stage. As you can imagine, finding random errors such as this in chips that fully pass stress and electrical error testing can be a daunting task, but finding the source of the issue can be an even more challenging endeavor.

Intel employs a range of testing techniques, including ultrasound, infrared, and sonar, to isolate defects and study the failed processors. After locating the defect, destructive methods, like grinding or using an ion beam, can be used to study the issue further. This information is fed back to the design teams to help develop newer steppings of processors or refine production production processes to stamp out recurrent bugs, if necessary.

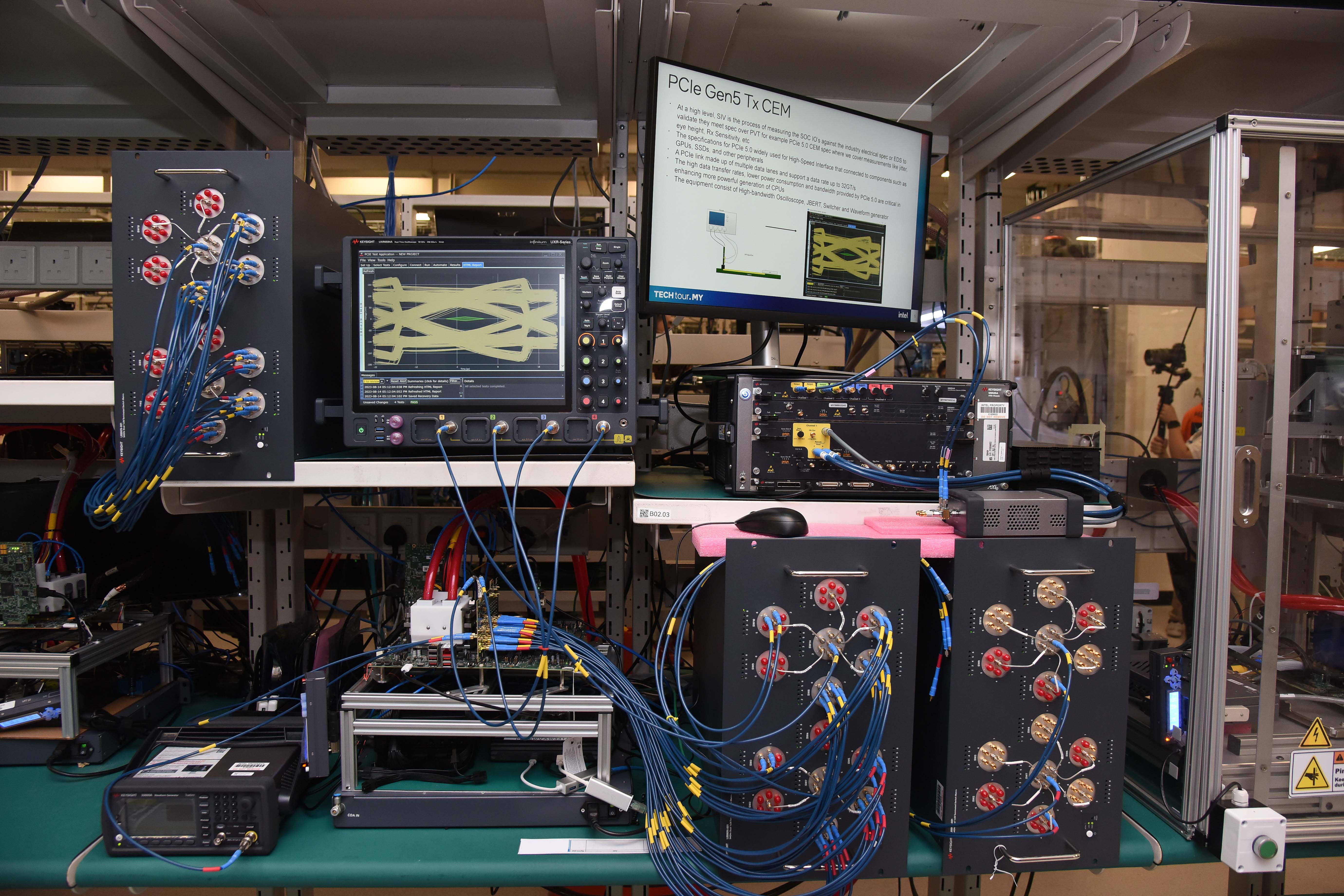

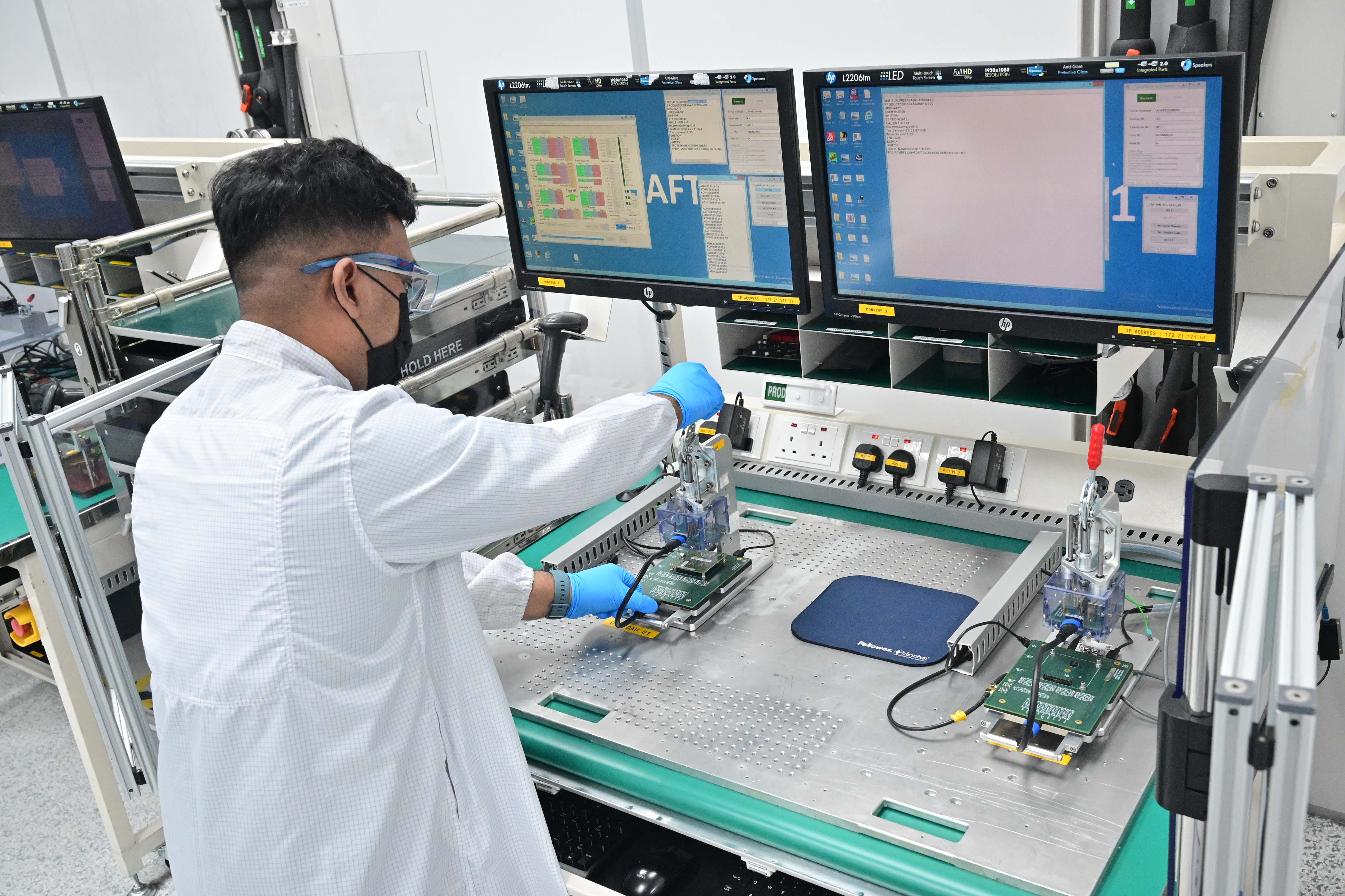

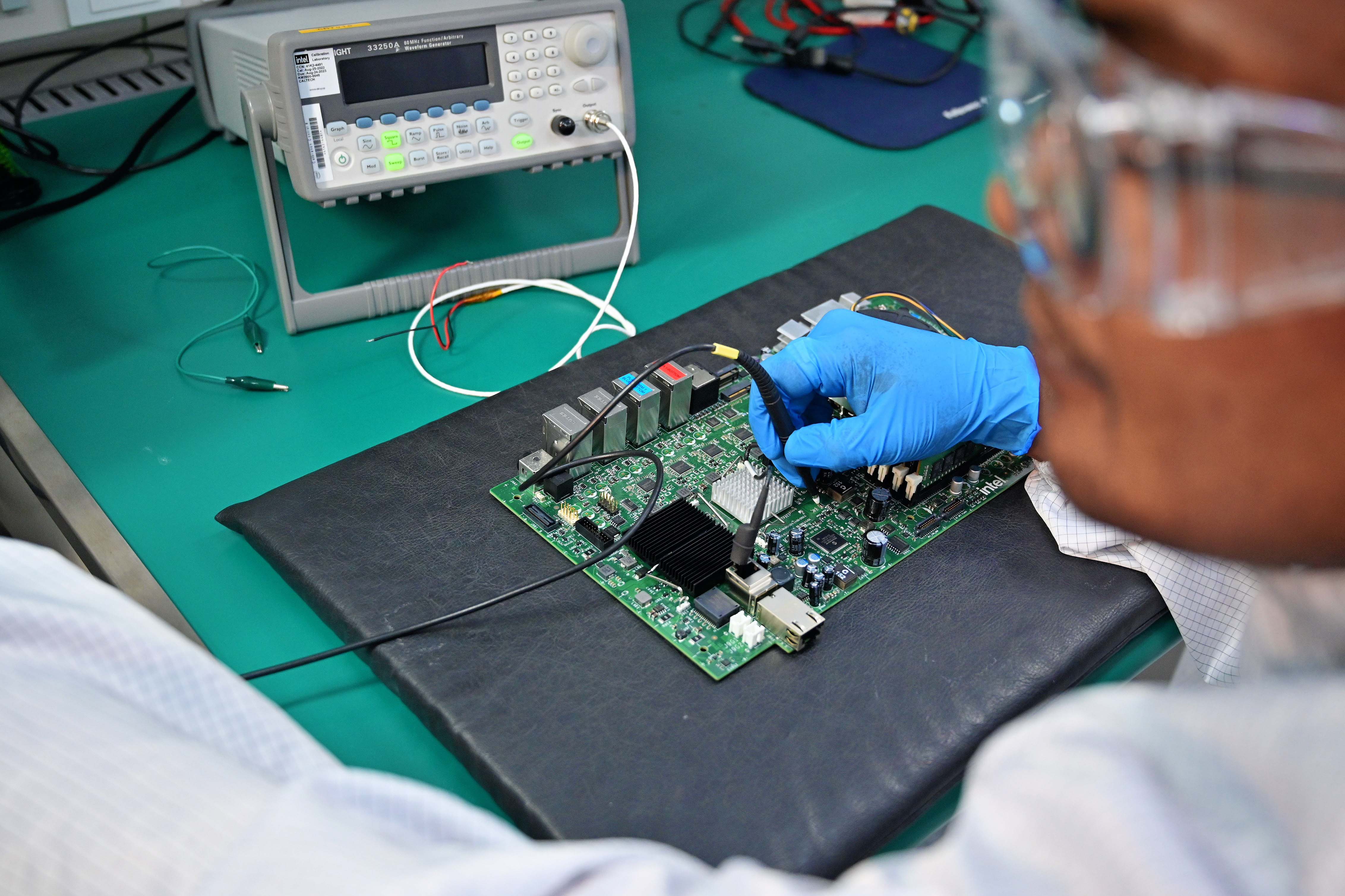

Article continues belowMalaysia Design and Development Lab (MDDL)

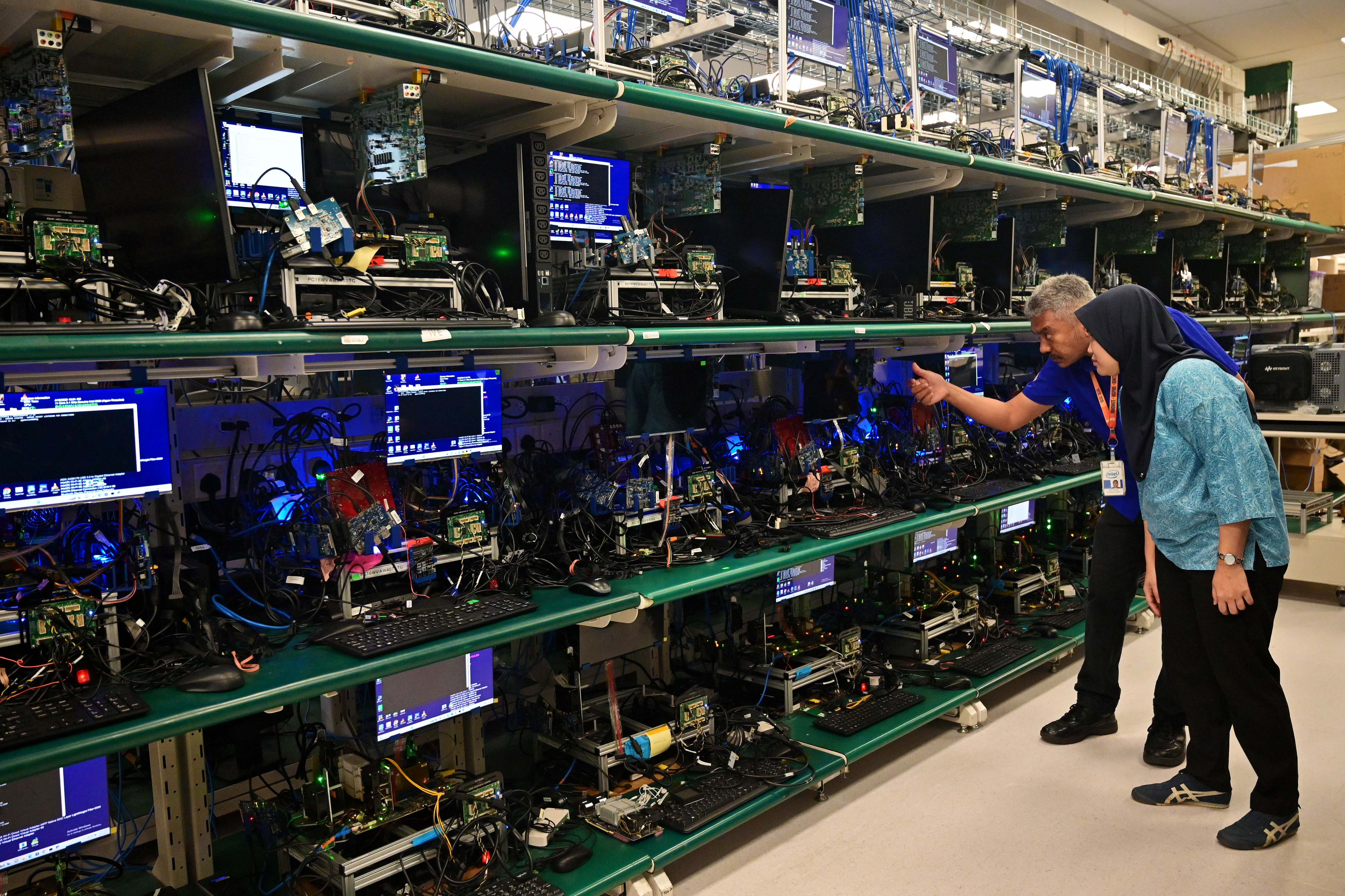

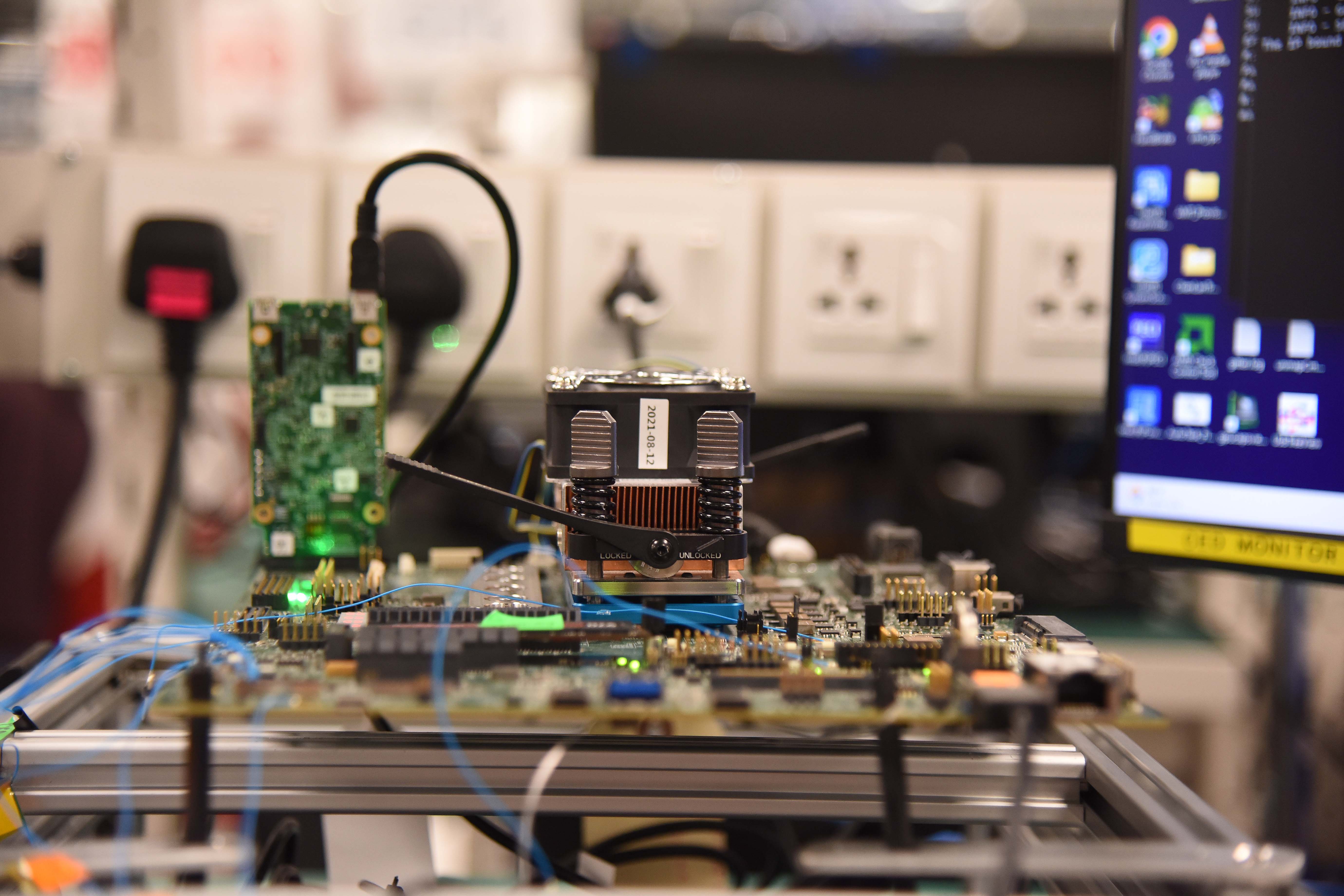

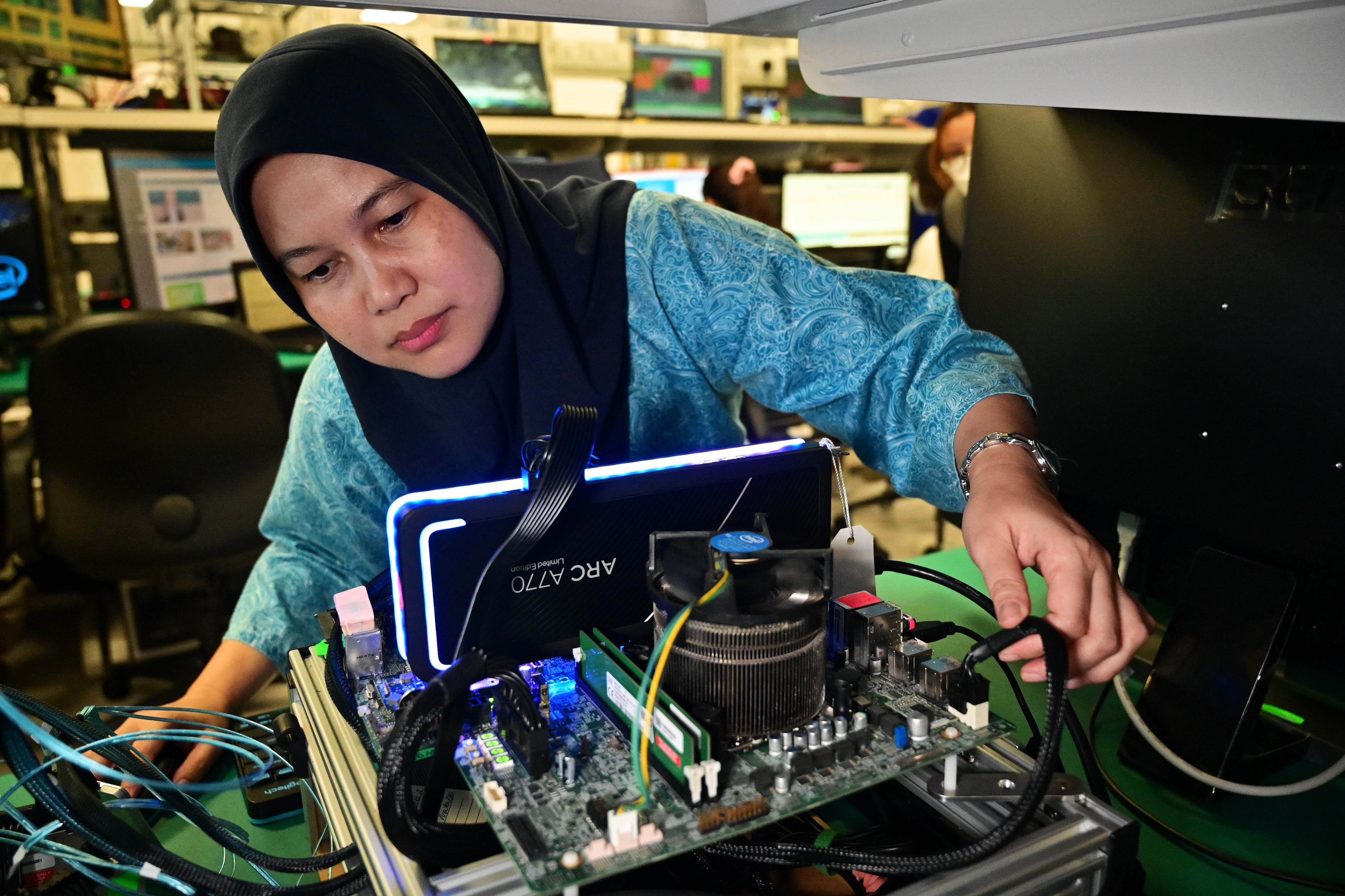

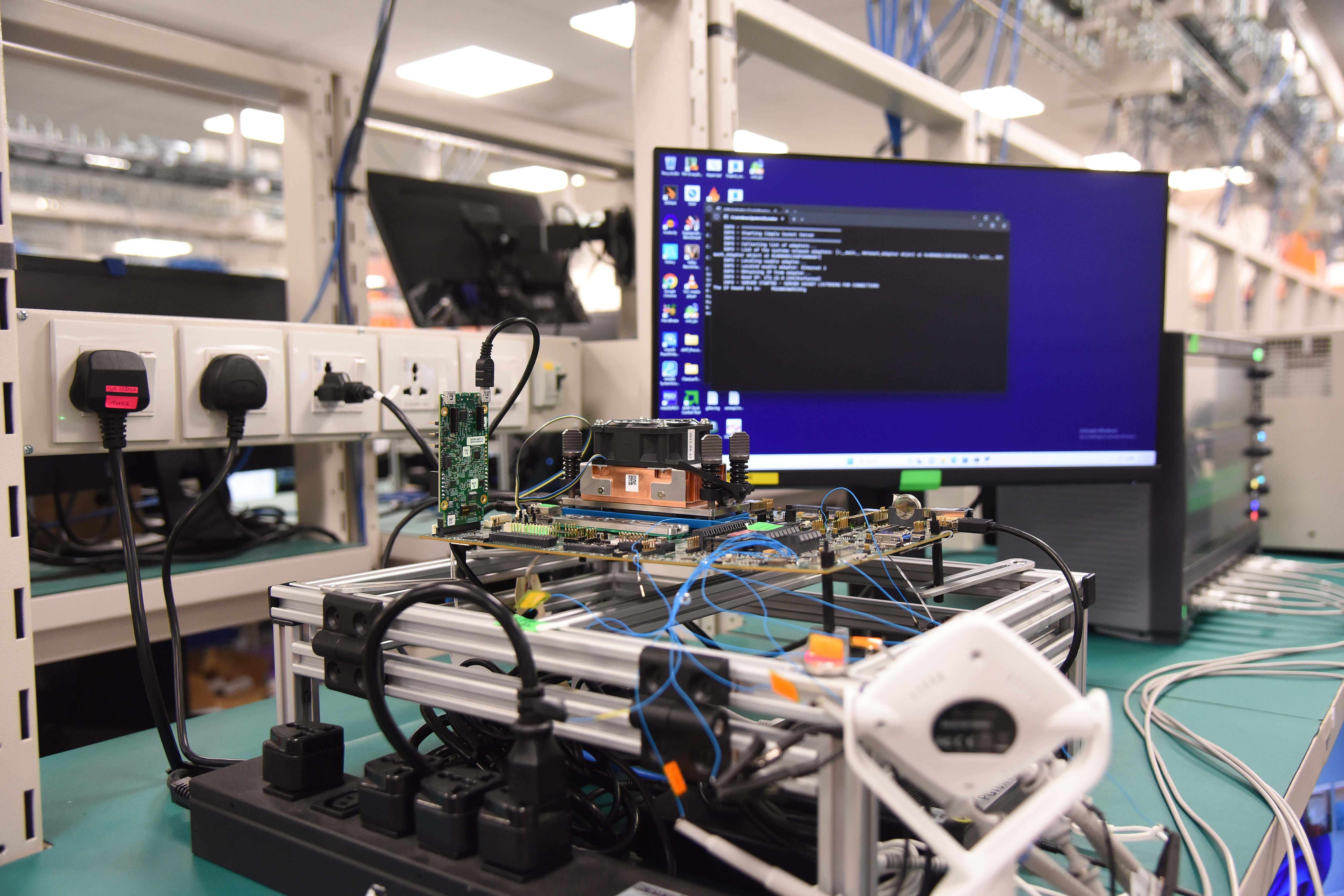

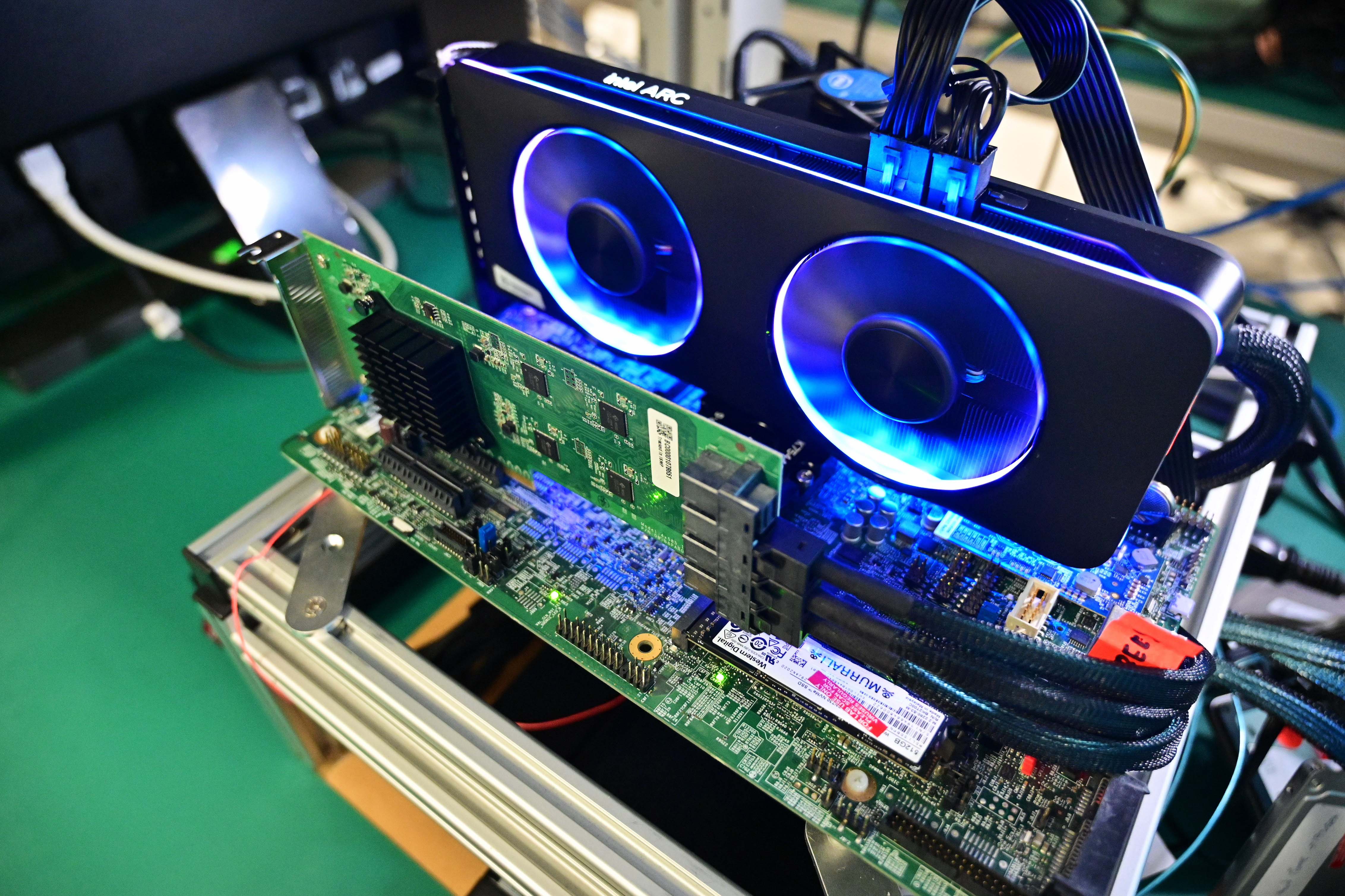

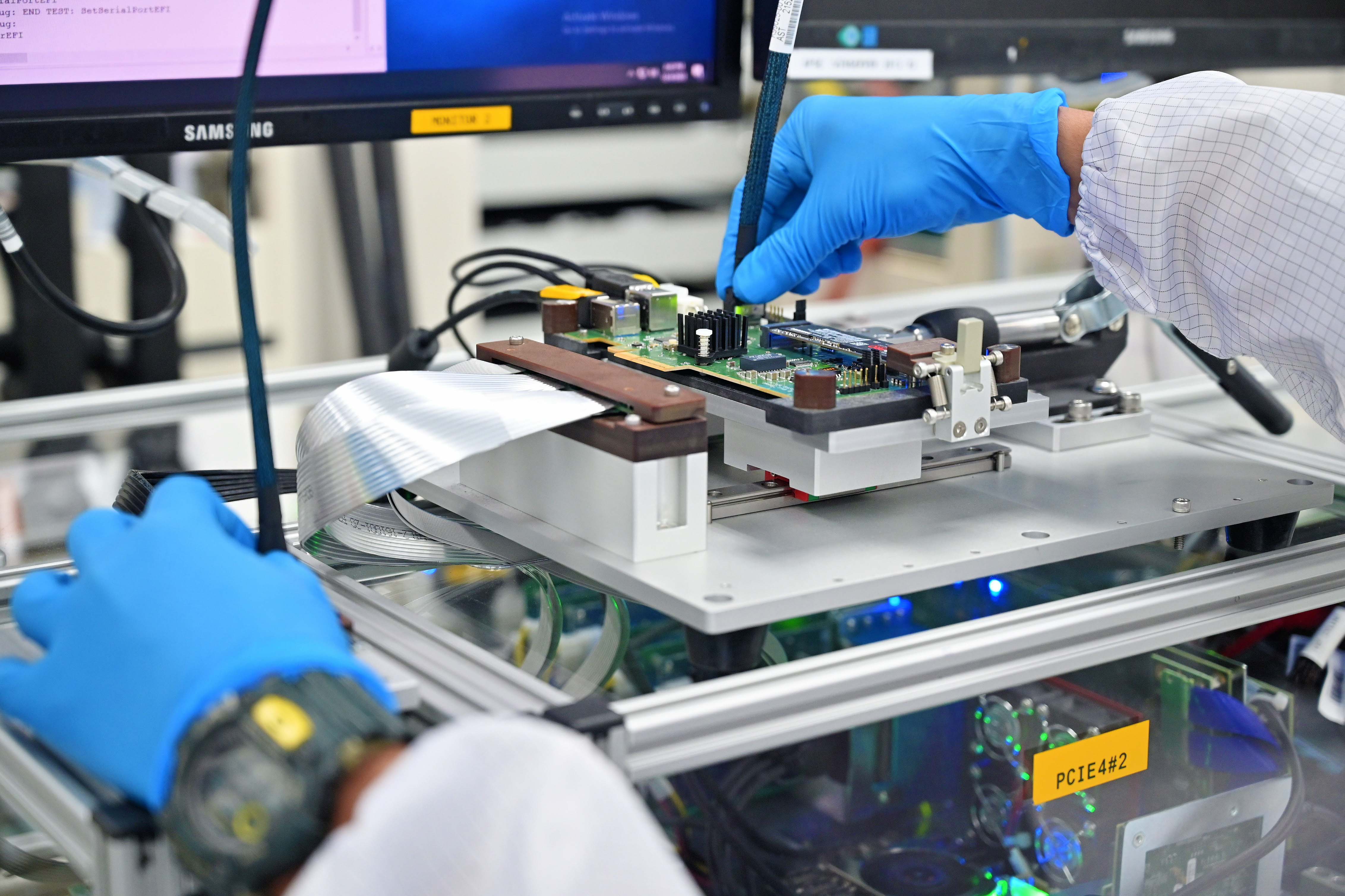

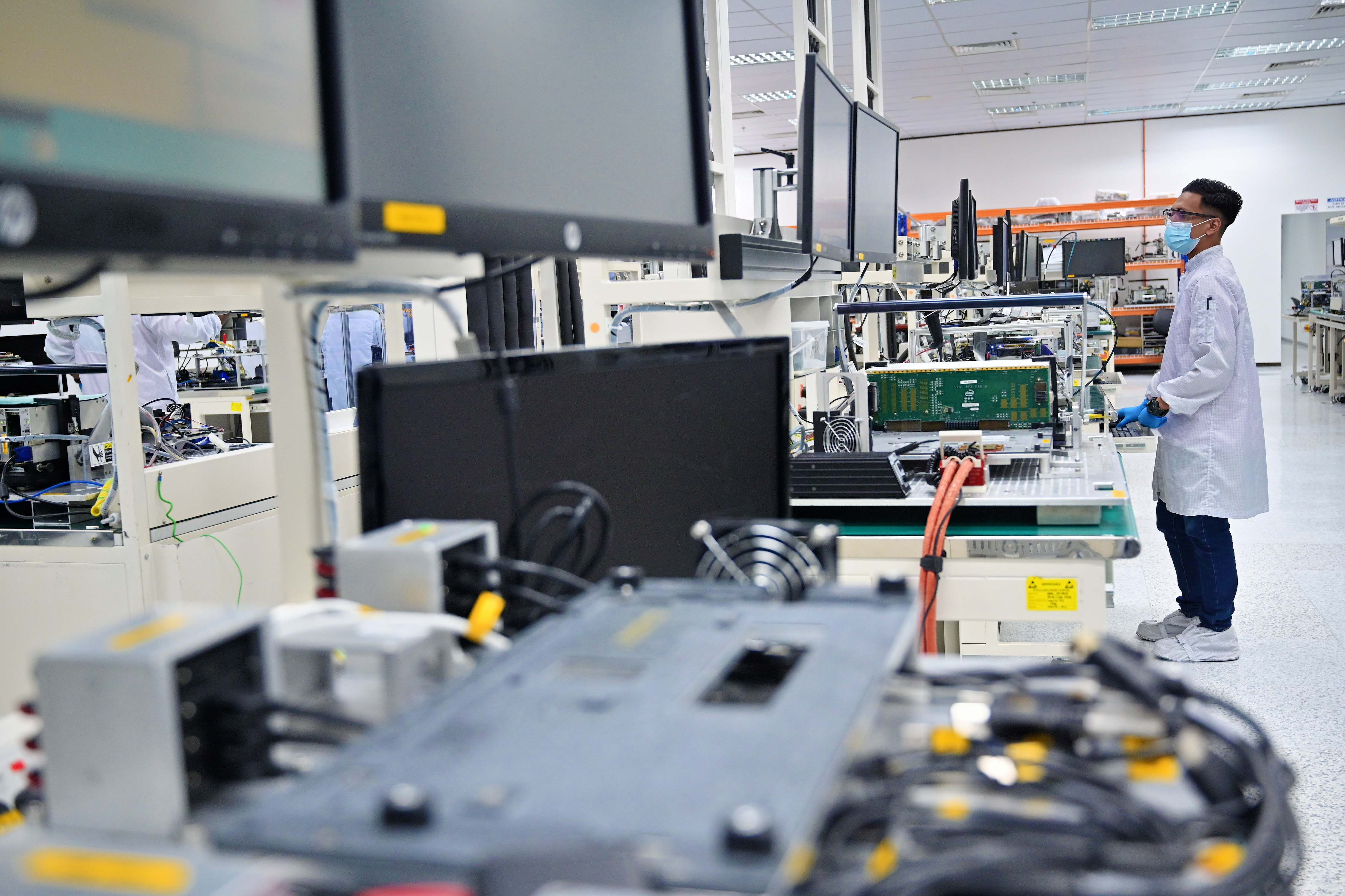

The Malaysia Design and Development Lab (MDDL) is responsible for large-scale testing to help validate new processor designs and IP. The teams in this area work on pre-release silicon and help validate core IP, like E-core and P-core silicon, SoC designs, and chipsets, by passing the chips through a barrage of real-world testing.

This team focuses on large-scale parallel testing to find any bugs in the new chips that come from Intel's research and development teams, ultimately helping to pave the way to mass production. This often includes fully stressing the device with every single form of I/O attached, like multiple monitors, GPUs, keyboards, mice, USB devices, Thunderbolt connections, storage devices, and other peripherals, all while conducting a series of stress tests under real-world operating conditions.

Unsurprisingly, this was one of the most closely guarded areas we saw on the tour. We were given a demo about Intel's future E-cores in a section that oddly had aisles upon aisles of empty shelves. We were told the systems in the area had all been removed prior to our arrival because they were testing unreleased products. Notably, this area was used for our 'Next-Gen E-Core' demo, so it's safe to assume the chips under test were of the Sierra Forest variety.

These teams are also responsible for power and thermal characterizations for new processors, helping to ultimately dial in the correct mixtures of voltage and frequency to assure stable operation. Other teams collaborate with Intel's customers to help them develop highly-tuned system designs to accommodate the newest chips, often by directly doing the tuning themself, other times by providing reference boards and designs.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

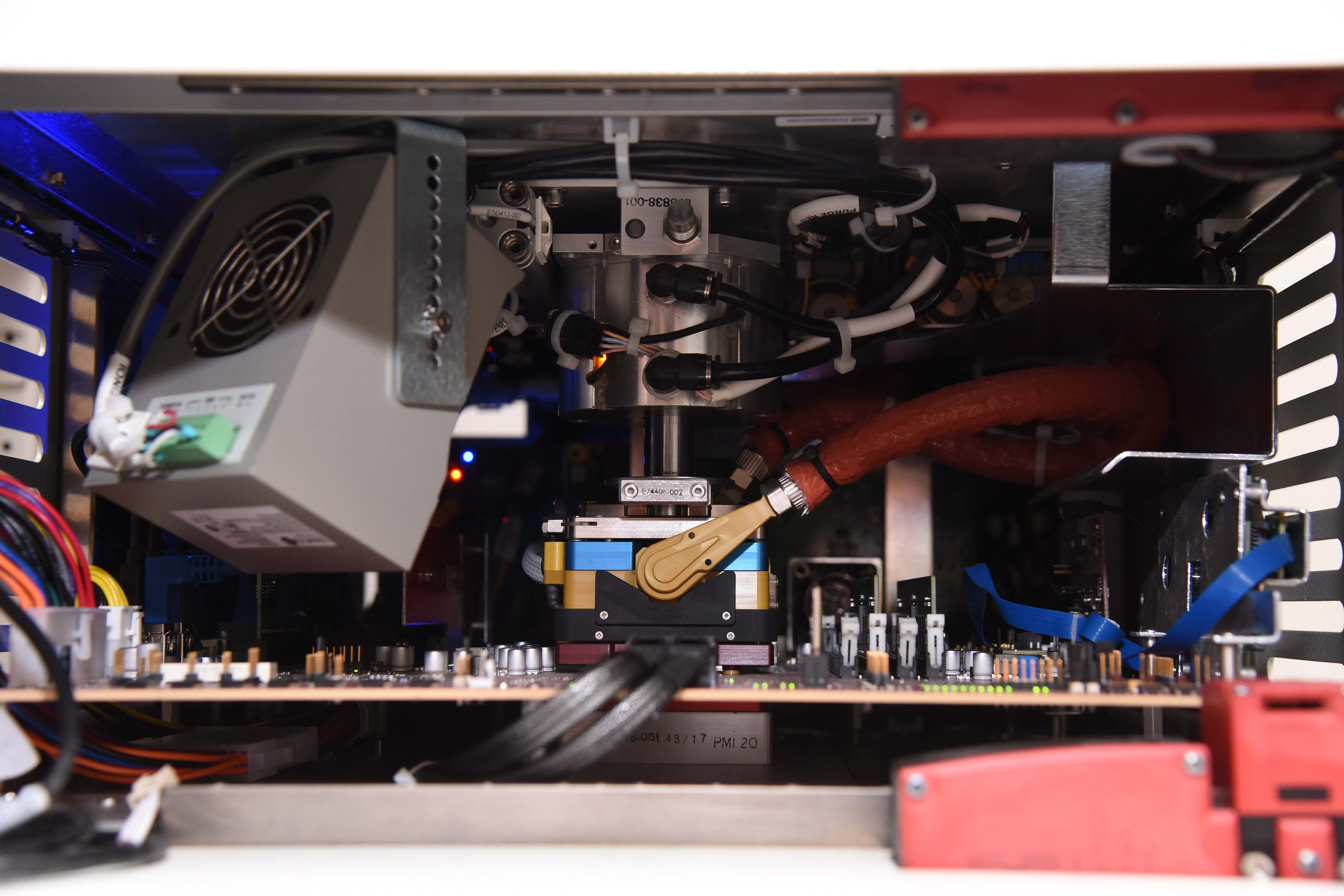

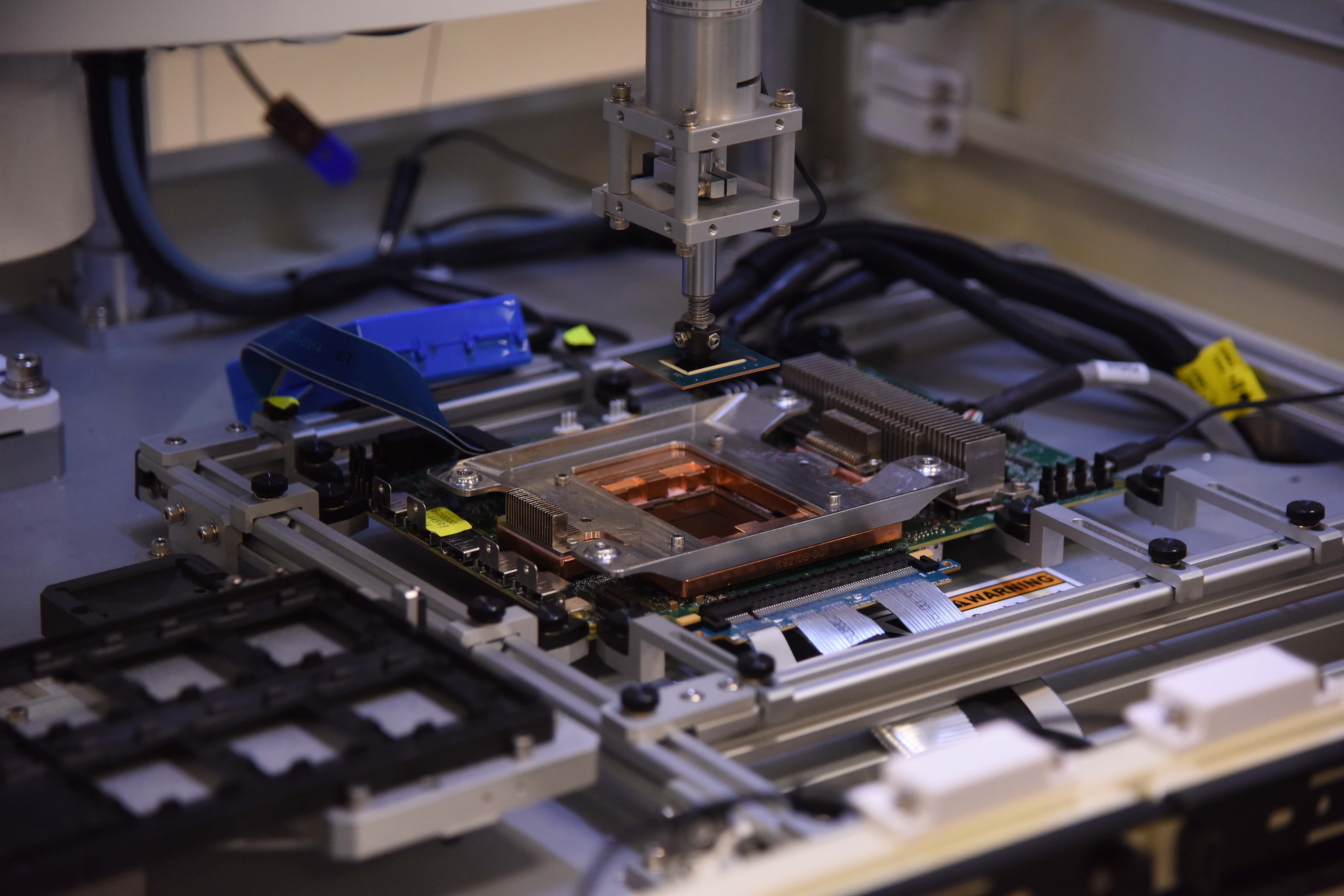

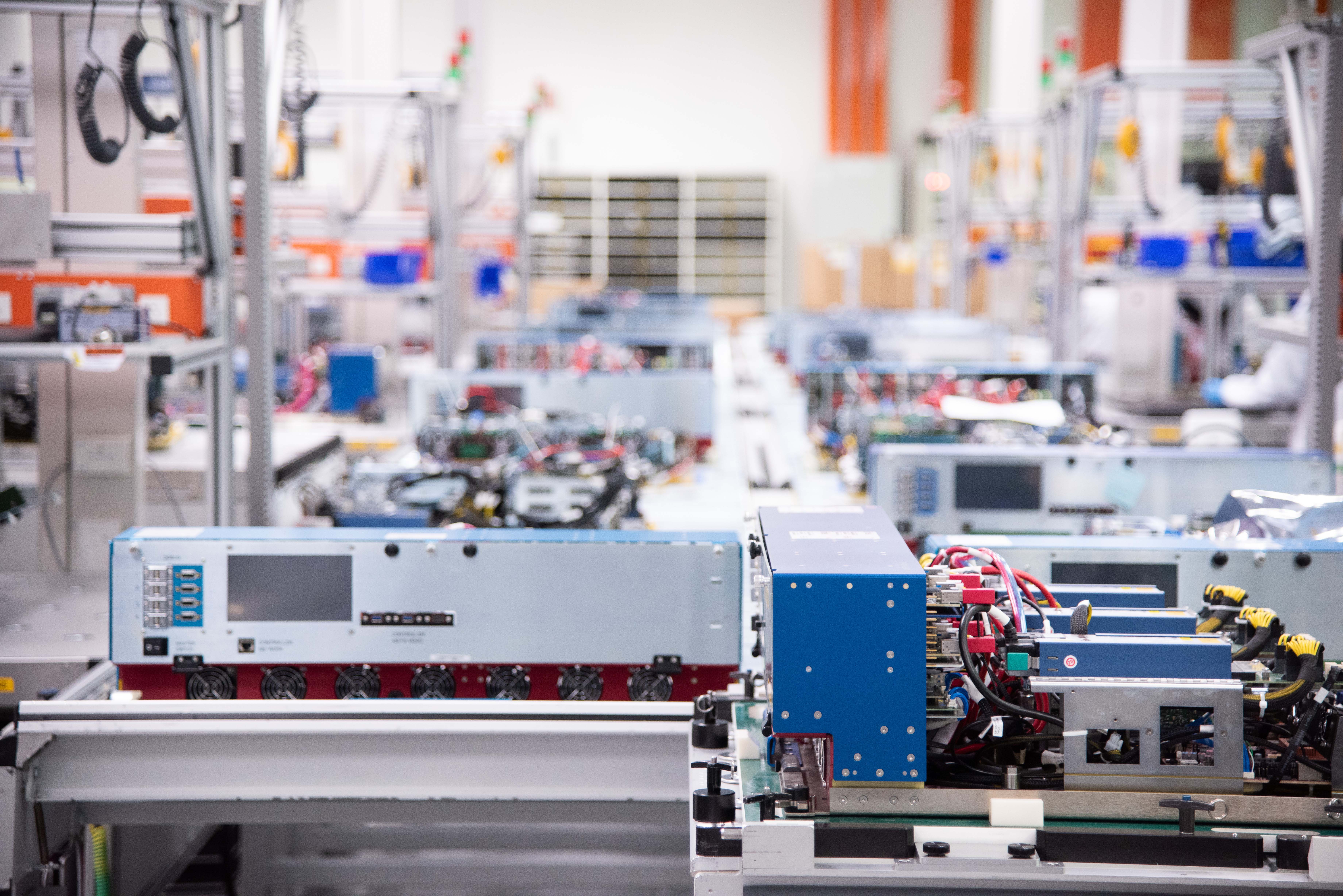

System Integration and Manufacturing Services (SIMS)

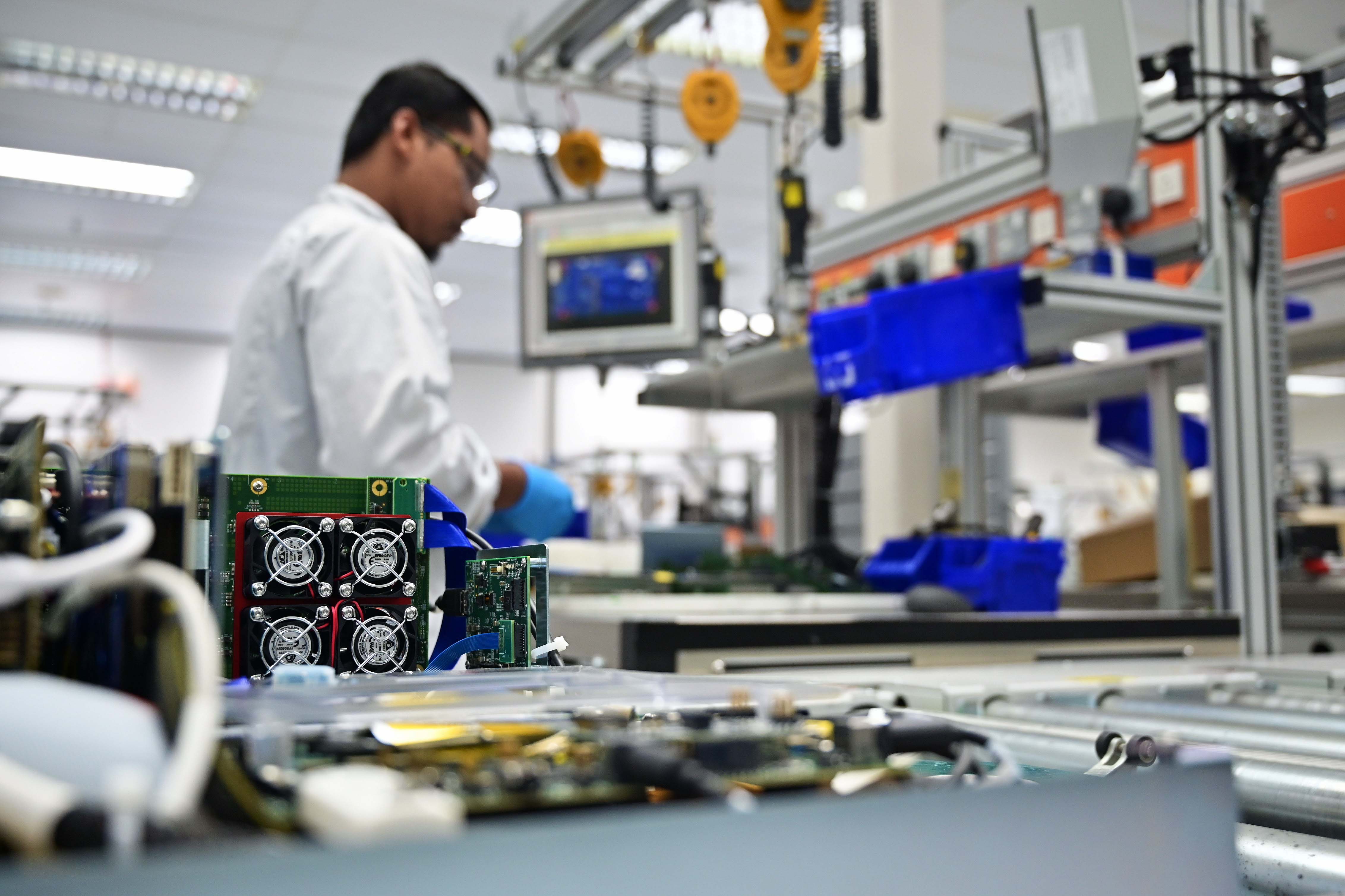

Unbeknownst to many, Intel has its own assembly line that creates high-tech testing devices for its facilities worldwide, and it's based in Kulim.

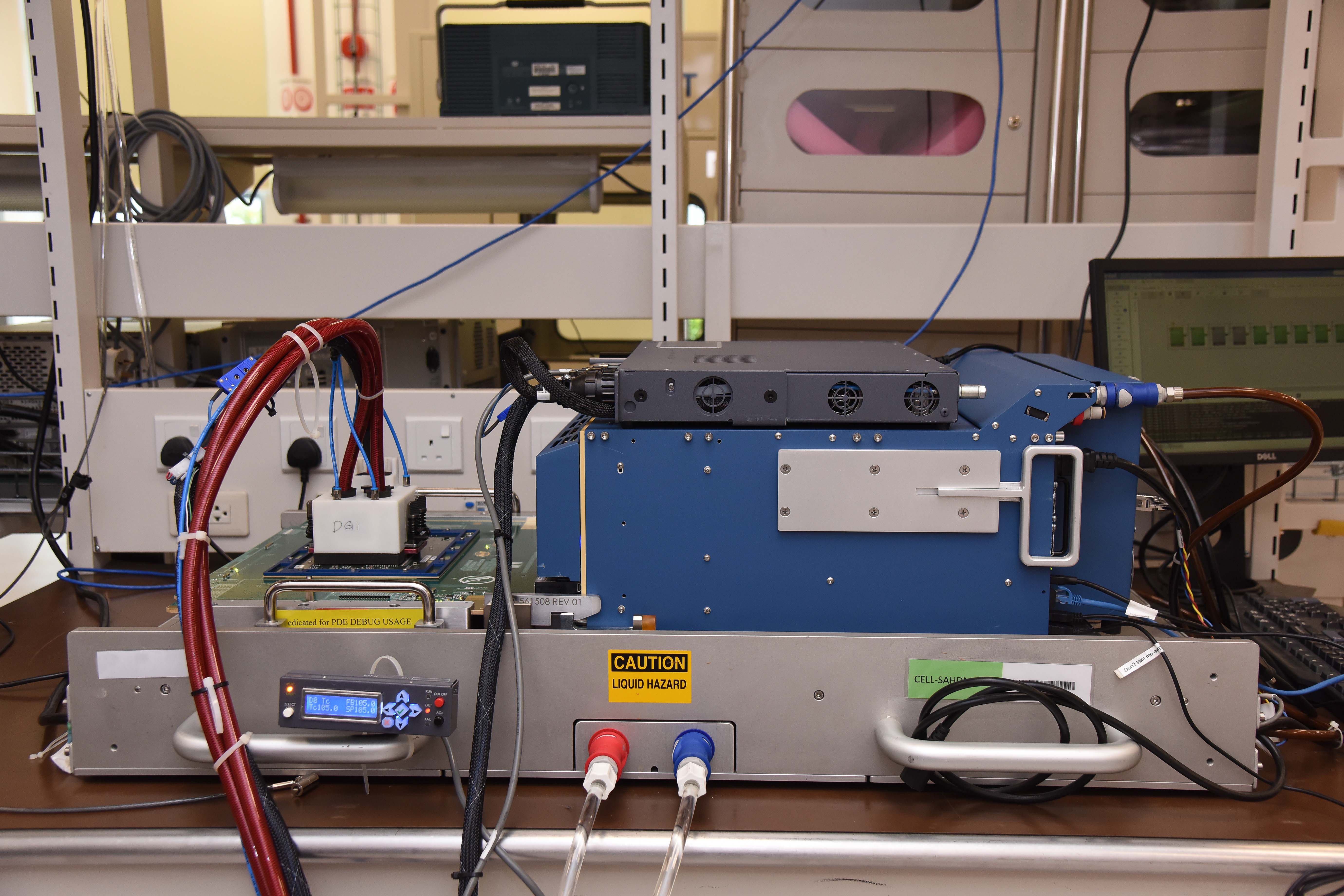

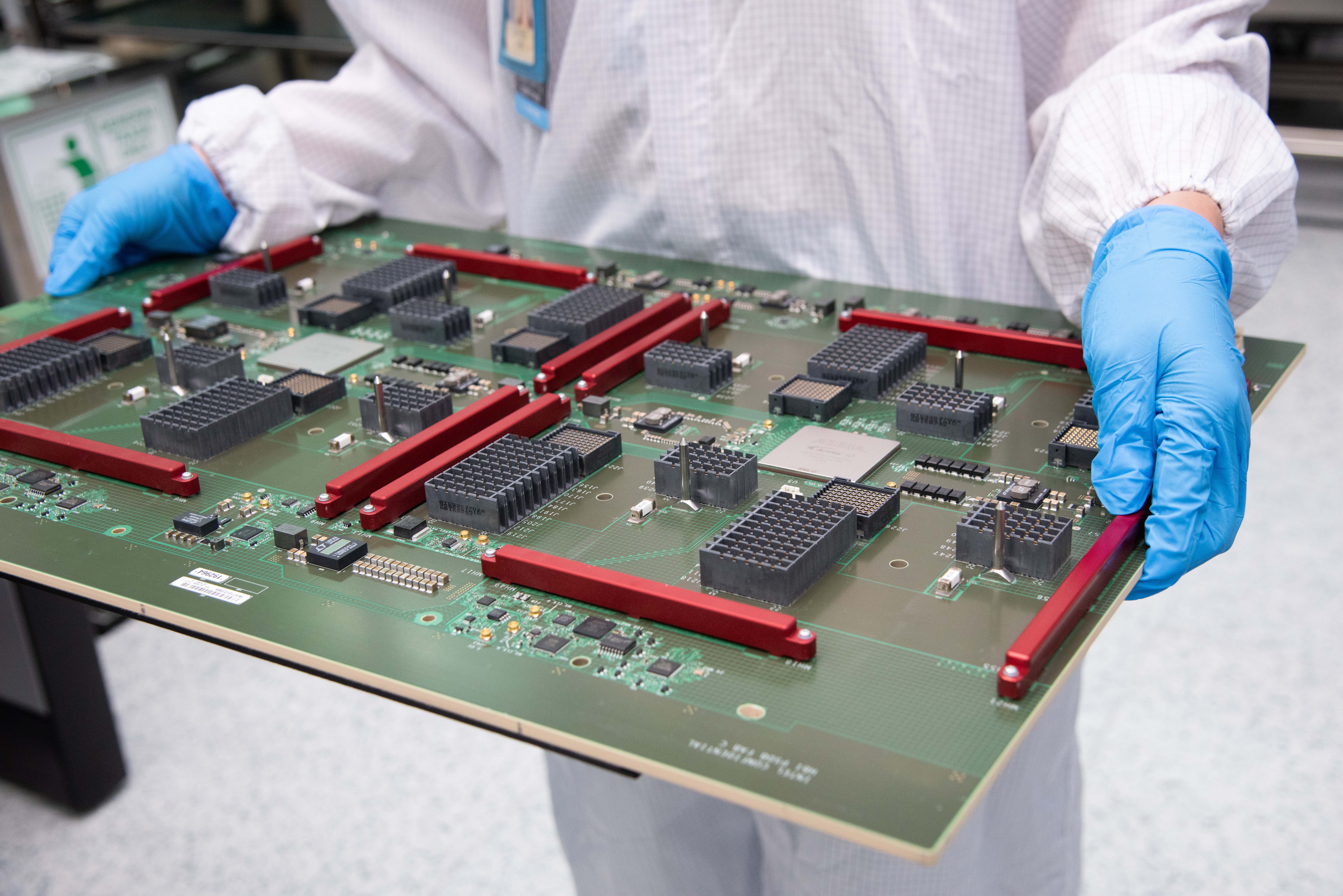

The System Integration and Manufacturing Services (SIMS) factory produces test equipment like Intel's High-Density Burn-in (HDBI) tester that's used for Burn-In stress testing for Intel's processors, as we outlined in the Assembly and Test section. You can see parts of that machine in the first six images in the album below.

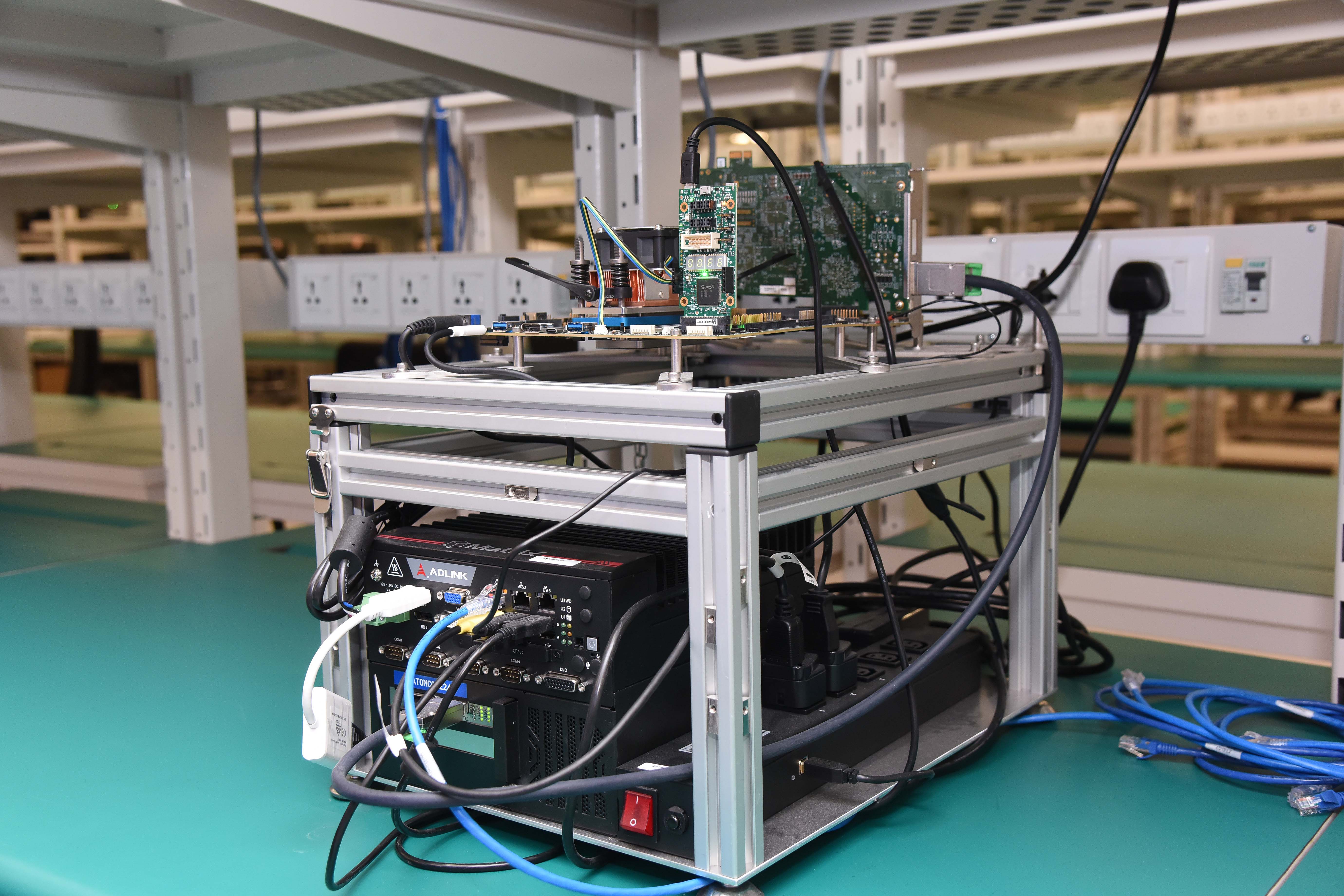

This group also the High Density Modular Tester that Intel uses to test and classify its chips before they're sent to be affixed to PCBs, and the System Level Tester machine that's used for testing under real-world conditions with actual operating systems and peripherals attached to the host system. That's pictured in the last image in the above album.

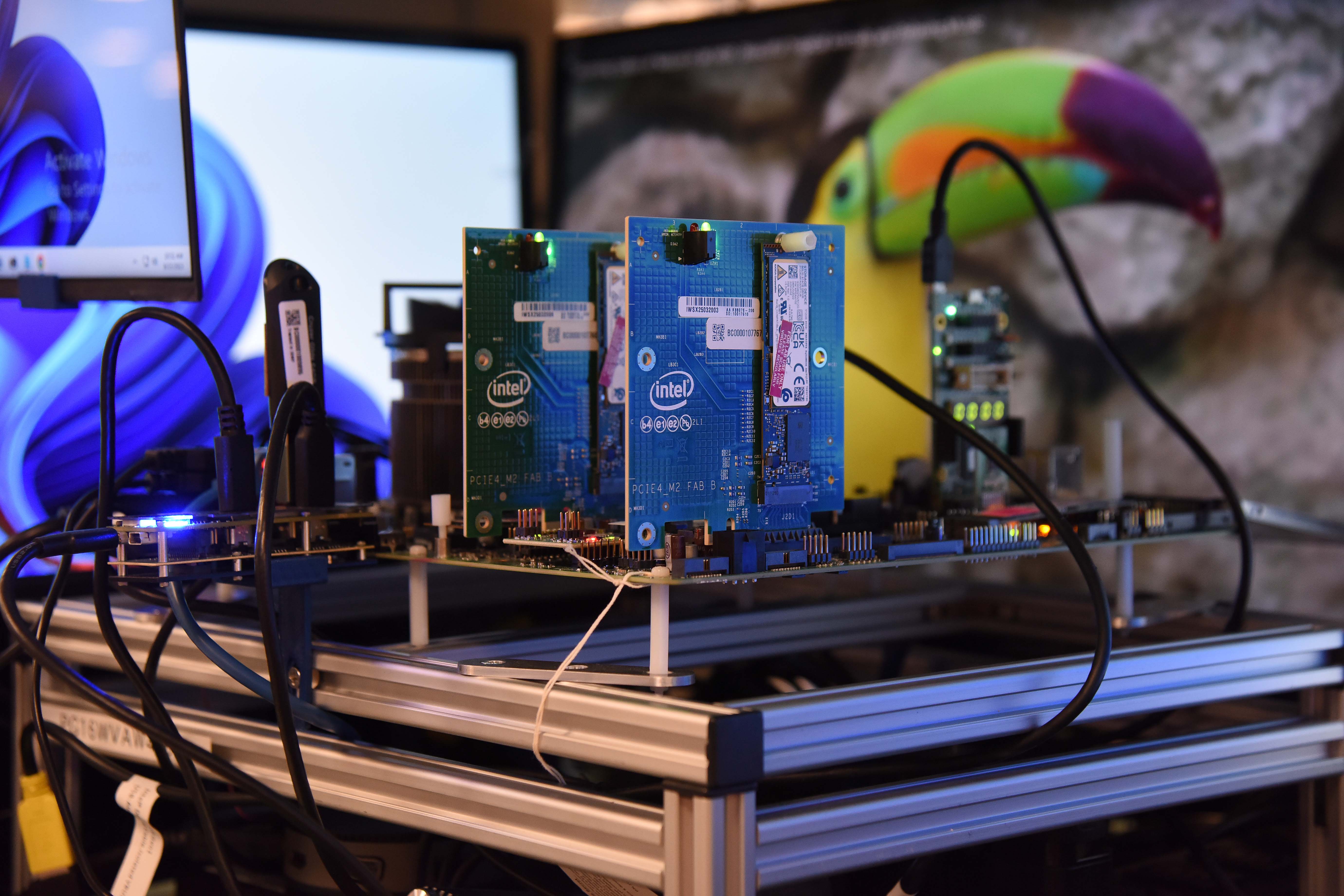

This group also creates Intel's Reference Validation Platforms (RVP), which are custom motherboards used during the development phase of any new chip. In fact, they manufactured the platforms we saw at Intel's Overclocking Lab a few years ago, not to mention a host of other equipment that Intel uses for testing its products at its global facilities.

These products are largely made with physical labor, there isn't a lot of automation in this area, but Intel manufactures these products itself to protect the development of its proprietary internal technologies.

Current page: Failure Analysis Lab, Malaysia Design and Development Lab (MDDL), System Integration and Manufacturing Services (SIMS)

Prev Page Penang Assembly and Test (PGAT) Next Page Final Thoughts

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

Roland Of Gilead "If successful, those advanced nodes will grant Intel the lead over TSMC for the first time in years, " - so, the reasoning being here, that TSMC will be standing by scratching their arses during this same period. And thus Intel will overtake them!? Okay.Reply -

Paul Alcorn https://fuse.wikichip.org/news/7375/tsmc-n3-and-challenges-ahead/Reply

Intel will match TSMCs std cell density with the Intel 4 process by the end of this year. After that, roadmap projections indicate Intel will pull ahead. -

jkflipflop98 ReplyRoland Of Gilead said:"If successful, those advanced nodes will grant Intel the lead over TSMC for the first time in years, " - so, the reasoning being here, that TSMC will be standing by scratching their arses during this same period. And thus Intel will overtake them!? Okay.

No, you just inserted your own thoughts. No one is saying TSMC is going to stand still. We're saying they aren't going to be able to keep up. -

vertuallinsanity Intel utilized TMSC as a stand-in *partner* during a period of machinery teething issues.Reply

The intention of that partnership, for certain products, was always temporary in nature or Intel would have gone fab-less similar to AMD. Intel utilized TSMC to prevent bring-to-market delay while simultaneously reworking their fab processes and equipment to a viable state.

The article seems to imply TSMC makes their own processors or gpus and they're in direct competiton with Intel. They don't and they arent.

TSMC and/or Intel may trade process enhancement "blows" but Intel makes Intel CPUs for Intel and TSMC makes 'em for "anybody".

The article implication could apply to Apple, NVidia, AMD or others competing with Intel on similar node products.

Intel will continue to work with TSMC on GPUs and other product lines deemed fiscally feasible. Intel and TSMC are still partners.

There is no way anyone from Tom's hardware was allowed a tour of Intel's new ish.

Fact.. -

Roland Of Gilead Reply

No, you just inserted your own thoughts, in relation to my post!jkflipflop98 said:No, you just inserted your own thoughts. No one is saying TSMC is going to stand still. We're saying they aren't going to be able to keep up.

If you didn't notice, this article is one sided! I did certainly enjoy the tour and article in relation to Intel's tech, but there is zero context as to why TSMC 'might' fall behind.

You are right, no one is saying TSMC is gonna fall behind, but without context how is a reader supposed to know that? By checking the forums posts for an addendum article that gives the reasons why TSMC might fall behind? A bit of balance to illustrate these comments would help. -

td47 It would be interesting to know how Intel prevents IP and manufacturing methods/secrets from being exfiltrated from the Chengdu facility in China - given that country's penchant f or stealing and copying the Western Tech to try to catch up!Reply