Researchers Build Open-Source SSD Controller That Surpasses 7 GB/s

A not so "academic" speed boost

Researchers lead by Professor Myung-Soo Jeong at the Korean Advanced Institute of Science and Technology (KAIST) have developed a new SSD controller that is able to surpass 7 GB/s in read speeds, as reported by FNN News. The controller is built using the OpenExpress standards, and its designs are available for free to universities and research institutes.

What's impressive about the 7 GB/s read speed is that very few SSDs available on the market nowadays achieve speeds anywhere near those. Theoretically, NVMe drives using four PCI-Express 4.0 lanes should be able to reach this figure, but today's commercial controllers haven't been able to saturate the PCIe bandwidth yet, with Phison's popular PS5016-E16 controller reaching around 5 GB/s at best.

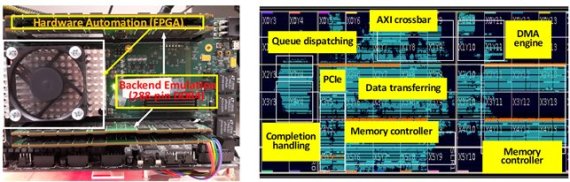

However, the SSD created by the researchers doesn't fit on a modern M.2 card like commercial SSDs. Rather, it is built on a custom FPGA, and notably bigger than the M.2 SSDs.

The creators only intend for the designs to be used by universities and research institutes as an alternative to expensive IP from the current offerings, as explained by professor Jeong: "There is no intention of breaking the industrial ecosystem that companies have, and only the school or research institute that has researched it has disclosed it."

So, you won't be able to buy this SSD on the open, consumer market -- if you want a 7 GB/s consumer-grade SSD, you'll have to wait a little longer.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Niels Broekhuijsen is a Contributing Writer for Tom's Hardware US. He reviews cases, water cooling and pc builds.

-

bit_user For me, the more interesting question would be what CPU core they used in it. Maybe RISC V?Reply

From the block diagram, it looks like it could be mostly hard-wired, though. That would explain where they get the speed, and could also limit its ability to run things like FTL and do certain housekeeping tasks. In which case, it would make sense why they're not looking to commercialize it.

...hmmm, more questions than answers. -

Deicidium369 Reply

No CPU core. It uses an FPGA.bit_user said:For me, the more interesting question would be what CPU core they used in it. Maybe RISC V?

From the block diagram, it looks like it could be mostly hard-wired, though. That would explain where they get the speed, and could also limit its ability to run things like FTL and do certain housekeeping tasks. In which case, it would make sense why they're not looking to commercialize it.

...hmmm, more questions than answers.

https://en.wikipedia.org/wiki/Field-programmable_gate_array

They are a research lab, and have released the designs as open source.

Maybe the Most Exalted Trump created a custom RISCV implementation - he is magic, you know. -

CooliPi Seem to me to be a proof of concept, using RAM as storage. Correct me if you see actual flash.Reply

It's useful even as it is, if the PHY and interface circuitry works, why not add any storage behind it. Garbage collection using any CPU is definitely welcome, depending on your non-volatile memory used (flash, optane, ...)

DRAM needs only self or controller helped refresh. Not a bottleneck in the whole design. -

bit_user Reply

I know what a FPGA is, thanks. Also, most larger FPGAs do have at least one CPU hard-core, but anyway...Deicidium369 said:No CPU core. It uses an FPGA.

https://en.wikipedia.org/wiki/Field-programmable_gate_array

What confused me is that the picture shows a FPGA, but then it also has a heatsink fan, under which I assumed was an ASIC. But you're right that a FPGA would make more sense for a university research lab.

This is just weird. I think you've misread me.Deicidium369 said:Maybe the Most Exalted Trump created a custom RISCV implementation - he is magic, you know.