SK Hynix, Intel Develop MCR DIMM: DDR5-8000+ for High-Capacity Modules

With some help from Intel, SK hynix's MCR DIMM combines extreme performance and capacity.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

When it comes to memory modules, there is usually a tradeoff between performance and capacity. But the novel MCR DIMM concept introduced by SK hynix and Intel on Thursday promises to wed extreme performance and capacity. The memory maker promises that its MCR DIMMs will enable data transfer rates of over 8000 MT/s, while offering unprecedented capacities.

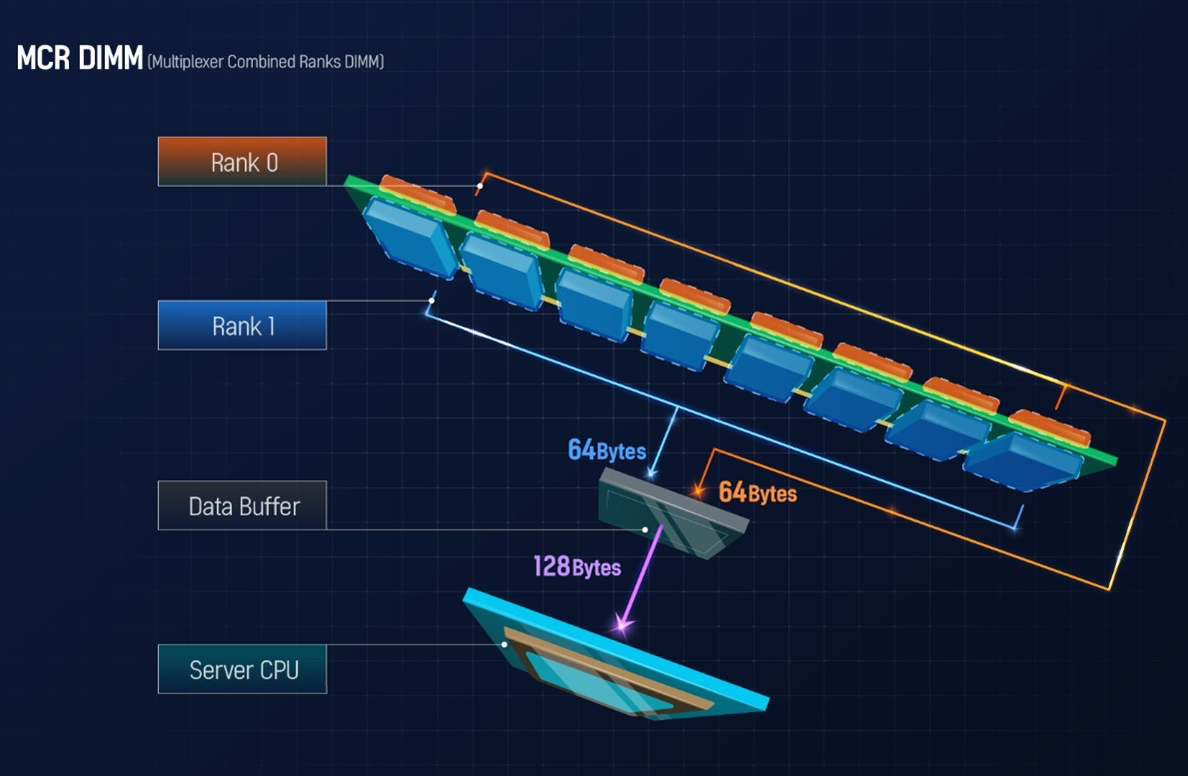

SK hynix's Multiplexer Combined Ranks (MCR) DIMMs are dual-rank memory modules that make both ranks work simultaneously using a special buffer. Normally, modules with two physical ranks work like one module, therefore when the host CPU (or memory controller) fetches data from such a module, it can only fetch 64 bytes of data at a time. But the buffer developed by SK hynix, Intel, and Renesas allows two physical ranks to work like two modules in parallel, thus doubling performance by fetching 128 bytes of data from both ranks at the same time.

The magic of the MCR technology is that both physical ranks (i.e., memory chips) of a dual-rank module continue to operate at more or less 'standard' clocks, which simplifies building high-capacity modules. Meanwhile, it is the Renesas multiplexer buffer that fetches 128 bytes of data from two modules and works at an 8000 MT/s or higher data transfer rate with the host CPU memory controller, again simplifying building high-speed modules.

Article continues belowAll buffers tend to increase latency and consume power, so these are the things that will have to be addressed both on the system and on the module level. Meanwhile, to make MCR DIMMs work smoothly, the technology has to be supported by the host CPU. So it is impossible to throw in an MCR DIMM into an existing machine hoping to get higher performance and higher capacity.

"For a stable performance of MCR DIMM, smooth interactions between the data buffer and processor in and out of the module are essential," said Sungsoo Ryu, SK hynix's Head of DRAM Product Planning.

Intel says that its future Xeon processors will support MCR DIMMs, but it does not disclose which CPUs will support the technology or when. Although the company has reportedly been working on this tech for a while. So one would hope the groundwork has been laid.

"The technology brought forward comes from years of collaborative research between Intel and key industry partners to produce significant increases in deliverable bandwidth for Intel Xeon processors," said Dimitrios Ziakas, Vice President of Memory and IO Technologies at Intel. "We look forward to bringing this technology to future Intel Xeon processors and supporting standardization and multigenerational development efforts across the industry."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

For now, MCR DIMM is largely a concept technology. SK hynix has confirmed that its MCR DIMMs can "operate at the data rate of minimum 8 GT/s." SK hynix has plans to bring the product to the market, but it does not say when this happens. Considering that the DRAM maker does not disclose any timeframes, it is hard to make predictions about the capacity of MCR DIMMs. But keeping in mind the capabilities of DDR5 SDRAM and the fact that MCR DIMMs are likely at least a couple of years away, we are probably talking about 1TB ~ 2TB modules.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

bit_user Reply

Given that it's not an Intel-developed technology, I doubt that will happen. SK Hynix will want to have it supported in ARM servers and AMD, as well.2Be_or_Not2Be said:Let's hope it becomes an open standard and not supported only by Intel Xeons.

I hope that by targeting server memory, they're somehow able to combine the buffer stage with the register used in RDIMMs, to avoid or minimize any additional latency.