Intel ships Nova Lake CPUs to partners for testing — samples intended for validation and research

We may soon encounter Engineering Samples in the wild.

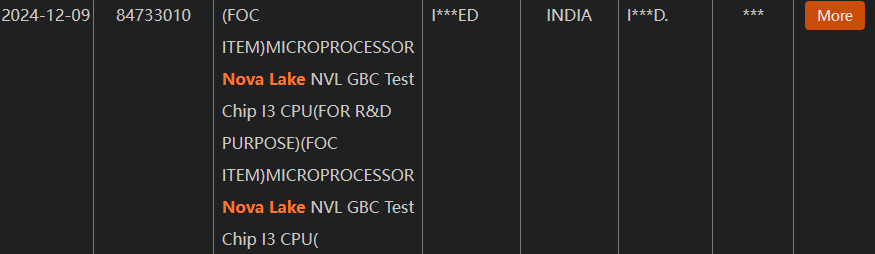

Shipping records indicate that Intel's Nova Lake chips are currently undergoing validation (via x86deadandback at NBD). Nova Lake is the successor to Intel's Arrow Lake series of processors and is expected to debut in 2026-27. While the manifests don't reveal any key details, it is essential to understand that final specifications are still subject to change.

Going by whispers in the wind, Nova Lake is rumored to employ Coyote Cove P-cores (renamed from Panther Cove) alongside Arctic Wolf E-cores. It is unclear where these architectures currently stand in Intel's product stack, so we cannot comment on any performance metrics. Ex-CEO Pat Gelsinger confirmed that most of Nova Lake will be produced in-house, likely on Intel 18A, with only a handful of SKUs expected to be outsourced.

The shipping manifest includes a single entry dating back to December 9th last year, reportedly marked as "FOC," which should stand for Free Of Charge. The listing explicitly tags the item as a "Microprocessor" and a "Test Chip" labeled "NVL," shorthand for Nova Lake. Last month, Wildcat Lake reball jigs surfaced similarly at NBD.

Arrow Lake suffers from poor L3 access latency due to an off-die memory controller and a slow ring bus which cripples performance in memory-sensitive applications. A leak alleges that Panther Lake will reintegrate the IMC (Integrated Memory Controller) back into the CPU Tile, similar to Lunar Lake. Likewise, Nova Lake is said to separate the two once again but with added optimizations.

Nova Lake is expected to require a new socket, and unless Intel ports Panther Lake to a desktop, LGA 1851 could be one of the shortest-lived platforms in Intel's history. In addition, Linux patches indicate Intel is actively developing software support for upcoming CPU generations, including Nova Lake and its supposed successor, "Razor Lake."

Next-gen E-core-only Clearwater Forest chips will feature Intel's "Local Cache" technology, designed to compete with AMD's V-Cache. CPU chiplets, expected to feature the cores and private caches, are placed on top of a Base tile. This Base tile can be configured with varying amounts of shared L3 cache. Sadly, this technology will remain exclusive to Intel's server counterparts for now but could someday make its way to consumer offerings.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Hassam Nasir is a die-hard hardware enthusiast with years of experience as a tech editor and writer, focusing on detailed CPU comparisons and general hardware news. When he’s not working, you’ll find him bending tubes for his ever-evolving custom water-loop gaming rig or benchmarking the latest CPUs and GPUs just for fun.

-

jheithaus Why would they move the memory controller off tile? They still are planning no vcache equivalent. Less cache than AMD with continued slower access. I understand cache costs money, but if you keep making vastly inferior products, you will be out of business because no one will buy your products. CRAZY.Reply -

TheSecondPower Reply

AMD's multi-chiplet CPUs have the memory controller off of the CPU chiplet, and Intel's tile architecture should be lower latency thanks to the base tile. On desktop Intel's solution is superior (evidently held back by other architectural details), but it's inferior to the monolithic chip AMD uses for mobile use. So why do it on mobile? For the same reason as before; better yields, lower cost, and earlier time to market, which helps to make up for Intel Foundry being behind.jheithaus said:Why would they move the memory controller off tile? They still are planning no vcache equivalent. Less cache than AMD with continued slower access. I understand cache costs money, but if you keep making vastly inferior products, you will be out of business because no one will buy your products. CRAZY. -

JamesJones44 Reply

The reason AMD doesn't put V-Cache on all CPUs isn't due to cost. Large caches can increase latency due to cache searches depending on the application. V-Cache works great for specific use cases where there is a high probability the content is in cache. However, for applications where cache misses are more prevalent it can be a hinderance if the miss occurs frequently. There are some other factors as well, such as cooling overhead, but cost isn't really the driver since we are only taking 10s of dollars.jheithaus said:Why would they move the memory controller off tile? They still are planning no vcache equivalent. Less cache than AMD with continued slower access. I understand cache costs money, but if you keep making vastly inferior products, you will be out of business because no one will buy your products. CRAZY.

Why Intel doesn't have their own "gaming" equivalent with a large cache is a question only Intel can answer. Does seem odd they would continue to seed gaming wins to AMD without some kind of an answer. -

thestryker Reply

Cost is absolutely the driver as the advanced packaging costs a lot more money and is another failure point. AMD has come out and stated that the reason they don't do cache on both CCDs for the two CCD parts is the cost vs benefit.JamesJones44 said:There are some other factors as well, such as cooling overhead, but cost isn't really the driver since we are only taking 10s of dollars.

It's actually super simple and straightforward: cost.JamesJones44 said:Why Intel doesn't have their own "gaming" equivalent with a large cache is a question only Intel can answer. Does seem odd they would continue to seed gaming wins to AMD without some kind of an answer.

Intel's designs until MTL were monolithic which means to add cache would require spinning up a separate die. Even now with tiles it wouldn't necessarily make financial sense as they would still have a separate die though the cost wouldn't be as bad as prior designs. CWF is using a design with cache in the base tile which might be viable to cross over to desktop, but this is the first Intel design hinting at anything cost effective for adding cache.

A lot of people also overestimate the retail market and X3D sales. I'd be surprised if if Intel didn't sell more desktop CPUs to Dell per year than AMD sells period. I'm absolutely certain the engineers at Intel would love to put together something faster, and marketing would love an easy win. That doesn't necessarily equate to it making financial sense to do so. -

Pierce2623 Reply

Somebody missed every article about market share in client systems over the last 3 years. Intel is no longer even selling more server chips than AMD.thestryker said:I'd be surprised if if Intel didn't sell more desktop CPUs to Dell per year than AMD sells period. I'm absolutely certain the engineers at Intel would love to put together something faster, and marketing would love an easy win. That doesn't necessarily equate to it making financial sense to do so. -

JamesJones44 Reply

That is for the due CCD, not CPUs as a whole. This is conflating two different things. Putting VCache on two CCDs probably doesn't provide much of a boost, thus cost to performance benefit isn't' worth it. However, as I mentioned, the price difference is small (10s of dollars), if it made a difference for every workload you better believe AMD would only make x3d series chips.thestryker said:AMD has come out and stated that the reason they don't do cache on both CCDs for the two CCD parts is the cost vs benefit. -

DS426 Reply

Cost isn't a significant difference but it does take more time to fully package V-Cache CPU's as well, something AMD acknowledged with their supply vs. demand constraints for the 9800X3D.JamesJones44 said:The reason AMD doesn't put V-Cache on all CPUs isn't due to cost. Large caches can increase latency due to cache searches depending on the application. V-Cache works great for specific use cases where there is a high probability the content is in cache. However, for applications where cache misses are more prevalent it can be a hinderance if the miss occurs frequently. There are some other factors as well, such as cooling overhead, but cost isn't really the driver since we are only taking 10s of dollars.

Why Intel doesn't have their own "gaming" equivalent with a large cache is a question only Intel can answer. Does seem odd they would continue to seed gaming wins to AMD without some kind of an answer.

I don't know how Intel could just ignore the success of the 9800X3D at this point and more generally this technology; with AMD having X3D chips that start not much over $200, even with not all games being able to take advantage of them, X3D is just a superior gaming CPU technology today when everything is considered, i.e. also bringing in the perf/watt conversation. I can understand Intel waiting a generation on for their Local Cache to come to desktop, but is that really something that can't be confirmed today? IMO, they've stripped the business back TOO much, being overly hyperfocused on safe CPU bets. -

TerryLaze Reply

AMDs main line (non cache) CPU have taken a huge hit in sales because everybody want's the cache ones, which are more expensive to make and have lower margins.DS426 said:I don't know how Intel could just ignore the success of the 9800X3D at this point and more generally this technology

Why would intel want that?!

Also the extreme PC buyer is a super small percentage, the average joe sees every CPU, including the entry level ones, hitting 100FPS+ in most games and so they don't care which has better FPS at over 9000 they buy whatever is cheap and readily available. -

thestryker Reply

You're absolutely right I missed the articles that don't exist!Pierce2623 said:Somebody missed every article about market share in client systems over the last 3 years. Intel is no longer even selling more server chips than AMD.

https://www.tomshardware.com/pc-components/cpus/amds-desktop-pc-market-share-skyrockets-amid-intels-raptor-lake-crashing-scandal-amd-makes-biggest-leap-in-recent-historyWhich of the numbers here is anywhere near 50% exactly?