Core 2 Duo Processor In Detail

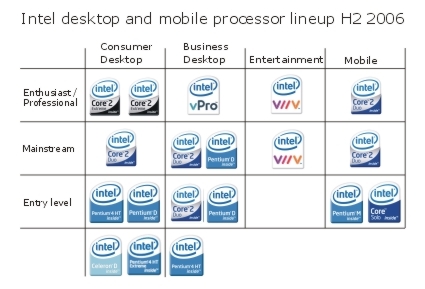

Intel's processor lineup for the second half of 2006 and early 2007. The consumer segment will be dominated by dual-core processors: Core 2 Extremes on the high-end (including the quad-core "Kentsfield" which is scheduled for Q4 of this year), Core 2 Duo

Intel’s processor lineup for the second half of 2006 and early 2007. The consumer segment will be dominated by dual-core processors : Core 2 Extremes on the high-end (including the quad-core "Kentsfield" which is scheduled for Q4 of this year), Core 2 Duo

A "Kentsfield"-based PC was first demonstrated by Intel in March of this year. The quad-core processor will be positioned on the very high-end of Intel's processor line-up and debut in Q4 of this year.

A "Kentsfield"-based PC was first demonstrated by Intel in March of this year. The quad-core processor will be positioned on the very high-end of Intel’s processor line-up and debut in Q4 of this year.

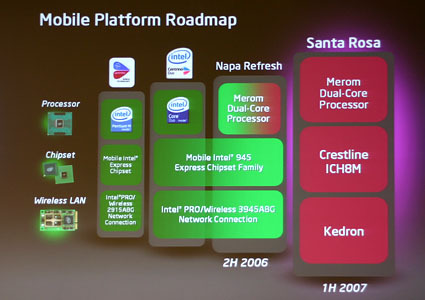

What's in store for Merom: Today, the Merom platform is simply called "Napa64" or "Napa Refresh" - basically a 64-bit version of the existing Core Duo platform. "Santa Rosa," due in Q2 of 2007, will be based on the "Crestline" chipset and bring several en

What’s in store for Merom : Today, the Merom platform is simply called "Napa64" or "Napa Refresh" - basically a 64-bit version of the existing Core Duo platform. "Santa Rosa," due in Q2 of 2007, will be based on the "Crestline" chipset and bring several en

The people behind Intel's Core micro architecture: Mooly Eden's design team is credited with the invention of the "Banias" processor. Eden's team developed the chip in Haifa, Israel. Today, Eden is vice president and general manager of Intel's mobile plat

The people behind Intel’s Core micro architecture : Mooly Eden’s design team is credited with the invention of the "Banias" processor. Eden’s team developed the chip in Haifa, Israel. Today, Eden is vice president and general manager of Intel’s mobile plat

David Perlmutter joined Intel in 1980 and led the team that worked on the first Pentium processor in the early 1990s. He was general manager of mobile platforms group in 2000 - in a time when the work one Banias processor began. Perlmutter became co-manag

David Perlmutter joined Intel in 1980 and led the team that worked on the first Pentium processor in the early 1990s. He was general manager of mobile platforms group in 2000 - in a time when the work one Banias processor began. Perlmutter became co-manag

Executive vice president Sean Maloney has held the top position in Intel's mobile business group for some time and directed the firm's mobile product strategy until recently. Maloney was promoted on 20 July to the position of chief sales and marketing off

Executive vice president Sean Maloney has held the top position in Intel’s mobile business group for some time and directed the firm’s mobile product strategy until recently. Maloney was promoted on 20 July to the position of chief sales and marketing off

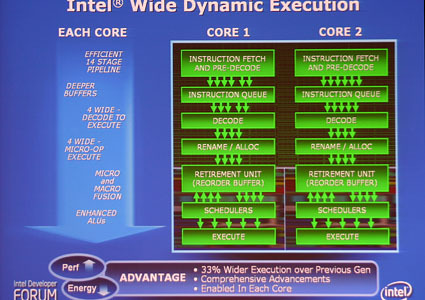

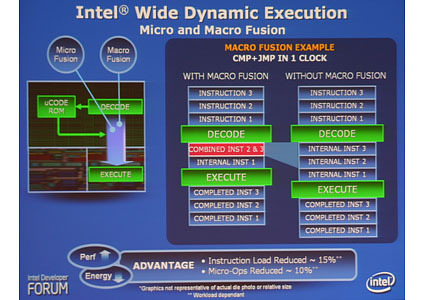

Intel highlights several new features in its Core technology. Among the three most significant is wide dynamic execution, which promises to improve processor performance and efficiency as each core can complete up to four instructions simultaneously using

Intel highlights several new features in its Core technology. Among the three most significant is wide dynamic execution, which promises to improve processor performance and efficiency as each core can complete up to four instructions simultaneously using

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

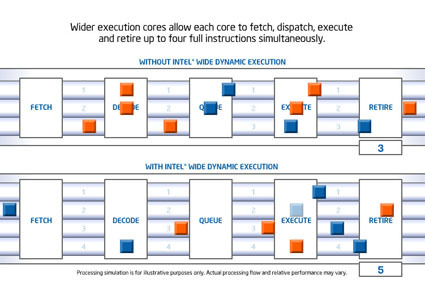

Illustration of wide dynamic execution.

Illustration of wide dynamic execution.

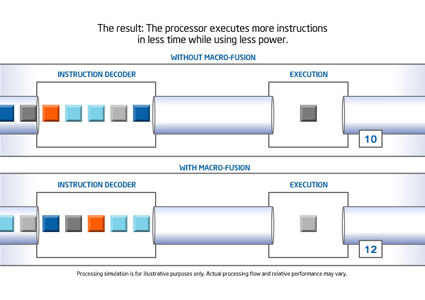

Another feature is macro fusion capability. Intel claims that it achieves a performance increase by combining two instructions to one instruction during the decoding process. This allows the processor to decode two instructions simultaneously.

Another feature is macro fusion capability. Intel claims that it achieves a performance increase by combining two instructions to one instruction during the decoding process. This allows the processor to decode two instructions simultaneously.

Illustration of macro fusion. Instructions are merged in the instruction decoder and processed as one instruction.

Illustration of macro fusion. Instructions are merged in the instruction decoder and processed as one instruction.

Tom's Hardware is the leading destination for hardcore computer enthusiasts. We cover everything from processors to 3D printers, single-board computers, SSDs and high-end gaming rigs, empowering readers to make the most of the tech they love, keep up on the latest developments and buy the right gear. Our staff has more than 100 years of combined experience covering news, solving tech problems and reviewing components and systems.