Hardware News: Catch Up Today!

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Analysis: Intel Six-Core Dunnington To Usher Out FSB

By Theo Valich - February 25, 2008

Vienna (Austria) - Intel's PR reps are recovering this week from GDC and are preparing for CeBit, which will open its doors next week. But there is a certain presentation about a relatively unknown part, which may keep Intel's phones ringing this week: Leaked information indicates that Intel's first hexa-core will debut this year.

It has not been a secret that 2008 will ring in the end of the front side bus at Intel. The company's Nehalem follows in the footsteps of AMD's K8 architecture (Opteron/Athlon 64), which introduced the Integrated Memory Controller (IMC) and Direct Connect Bus (HyperTransport), which provides offers a complex design that, in theory, represents the most efficient CPU design available today.

However, before the FSB will disappear for good, there will be one more siginificant chip using this structure: Meet Dunnington, Intel's first native multi-core chip. If AMD's definition of "multi-core" is correct, then "multi" indicates a number greater than two (three-core AMD Phenom 8000 series, four-core Phenom 9000, etc). In that case, Intel is set to offer 50% more cores than AMD currently has.

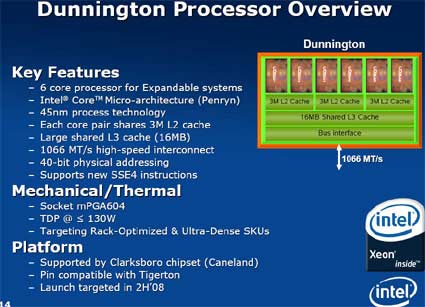

According to a leaked presentation, Dunnington will be last CPU coming out of the Penryn generation and will surface as a single-die six-core chip. This processor is geared for high-integrated systems such as blade servers. Socket-wise, the CPU uses mPGA604 and is pin-to-pin compatible with Tigerton.

To us it looks like this processor is sheer evidence of just how scalable the original Conroe architecture (introduced in 2006) turned out to be. All three dual-core segments in Dunnington have their own L2 cache (3 x 3 MB), which leads us to believe that we are seeing here three Wolfdale (45nm dual-core) dies bolted together. The CPU also integrates 96 kB L1 cache (Data) and 16 MB of L3 cache. The power consumption is considerable, but at least below 130 watts. Looks like Intel is preparing another processing monster.

Given the fact that Dunnington will use the Caneland chipset and has the complexity of a single-die design, we're not surprised that Intel engineers opted for a front side bus clocked at 1.06 GT/s (or "GHz"). So, we are talking about 266 MHz QDR (Quad Data Rate) clock, which is used on most Intel Core 2 based processors.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

This processor is coming to market in blades and other stacked designs from Sun Microsystems and other Intel partners. Release date is second half of this year, or just a nice warm-up for a monster we known under the codename Nehalem.

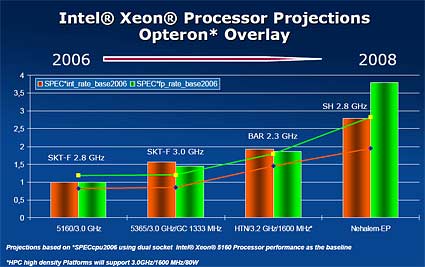

Intel also provided some information about the potential performance of Nehalem. Depending on the benchmark, Nehalem could be more than three times faster than a Woodcrest 3.0 GHz chip (Xeon 5160). Intel claims that a 2.8 GHz Nehalem CPU will outrun the Woodcrest chip by a factor of 2.8 in SPEC int_rate_base2006 and by a factor of 3.8 in SPEC*fp_rate_base2006.

Current page: Analysis: Intel Six-Core Dunnington To Usher Out FSB

Prev Page Qimonda Says Its on the Way to 30 nm DRAM Next Page Fujitsu Announces 500 GB Notebook Hard DriveTom's Hardware is the leading destination for hardcore computer enthusiasts. We cover everything from processors to 3D printers, single-board computers, SSDs and high-end gaming rigs, empowering readers to make the most of the tech they love, keep up on the latest developments and buy the right gear. Our staff has more than 100 years of combined experience covering news, solving tech problems and reviewing components and systems.