Gelsinger fires back at recent stories about 18A's poor yields, schools social media commenters on defect densities and yields

Former Intel chief executive Pat Gelsinger believes in the company's 18A process technology.

Having joined Intel at a tough time and doing his best to revive the company before retiring, Pat Gelsinger is yet to see the fruits of his decisions as the chief executive of Intel. However, based on his claims, the 18A process technology — the pinnacle of his five nodes in four years plan — is a success. Being ousted by the board, Gelsinger now has more time to respond to messages on X, which adds some color to what's happening with Intel's node development.

Pat Gelsinger responded to Patrick Moorhead's post claiming that a rebuffed story about Broadcom being disappointed with Intel's 18A due to low yield was 'fake news.' The original story emerged in early September, right after Intel's then-CEO Pat Gelsinger disclosed the defect density (D0) of 18A, which back then was 0.4 def/cm^2.

"I am so very proud of the TD/18A team for the incredible work and progress they are making," Gelsinger wrote in an X post.

Given that 18A was several quarters away from mass production at that time, such a defect density was good enough, though worse than that of TSMC. For instance, the defect density of TSMC's N7 and N5 fabrication processes was about 0.33 def/cm2 three quarters before mass production, which was the same point where Intel's 18A was in early September.

It is commonly believed that a defect density below 0.5 defects per square centimeter is good (0.5 def/cm^2), though when it comes to the yield of actual chips, everything depends on the size of the die.

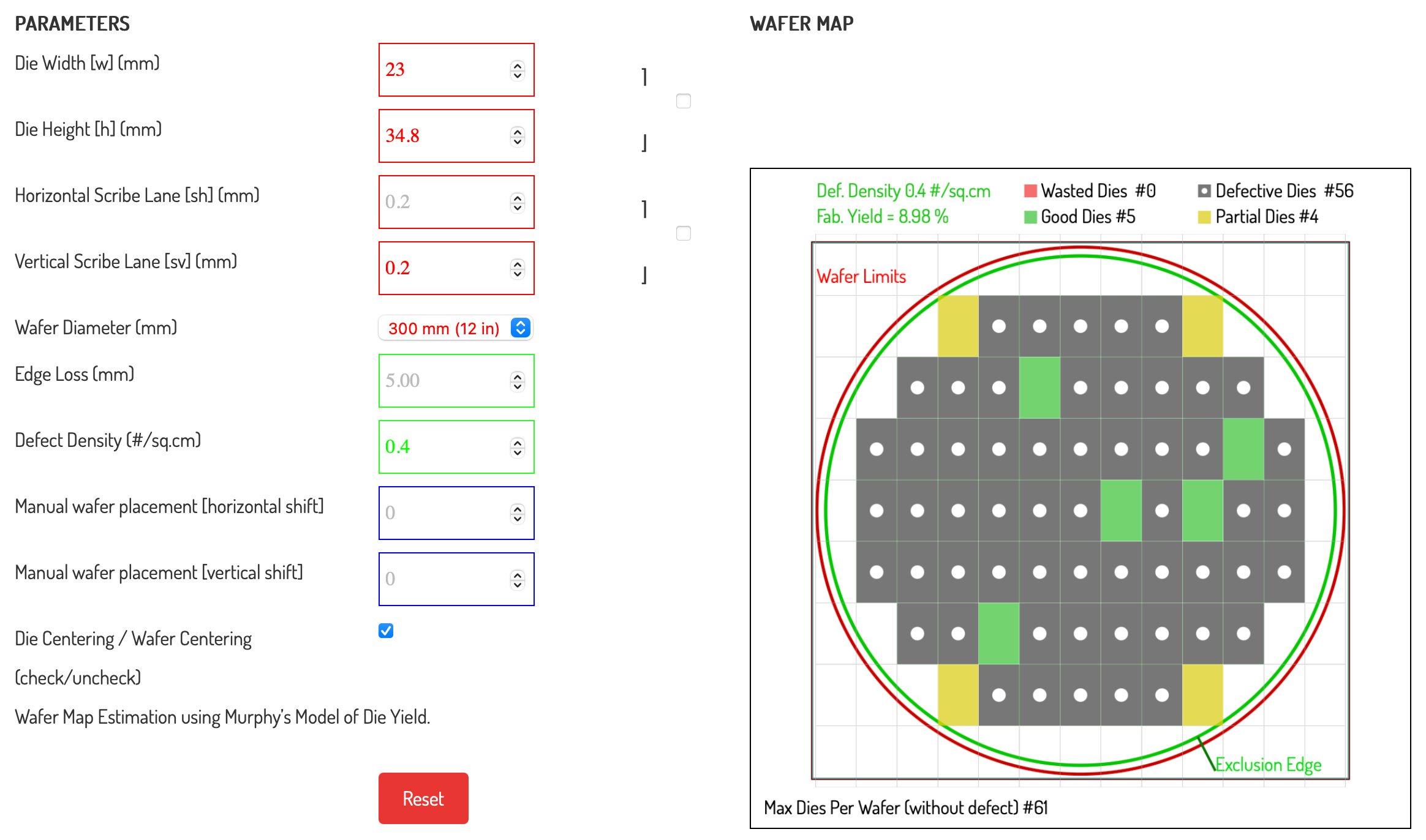

Broadcom is known for its gigantic system-in-packages for AI with compute chiplets close to the size of a reticle, which in the case of EUV lithography tools is 858 mm^2. Let's assume we are dealing with 800 mm^2 dies, which is the size of one Nvidia's Blackwell GPU chiplet (there are two chiplets per B100/B200 processor). In this example, there are 59 - 65 die candidates on a 300-mm wafer (assuming that we are dealing with a hypothetical 23 ´ 34.8 mm die), depending on various parameters. With a defect density of 0.4 def/cm^2, that gives us five perfect dies per wafer at a yield of around 9%. In the case of a defect density of 0.2 def/cm^2, we are already talking about 15 perfect dies and a yield of 24.9%.

There are several catches to be aware of in such a calculation. First, both Broadcom and Nvidia implement huge redundancies in their designs, so even with a relatively high defect density, they can get enough sellable die to justify the production of a 300-mm wafer using an advanced node. Depending on the client and contract, this might be at $20,000 per wafer, which means that their actual yield is well above the one we got from a publicly available yield calculator.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

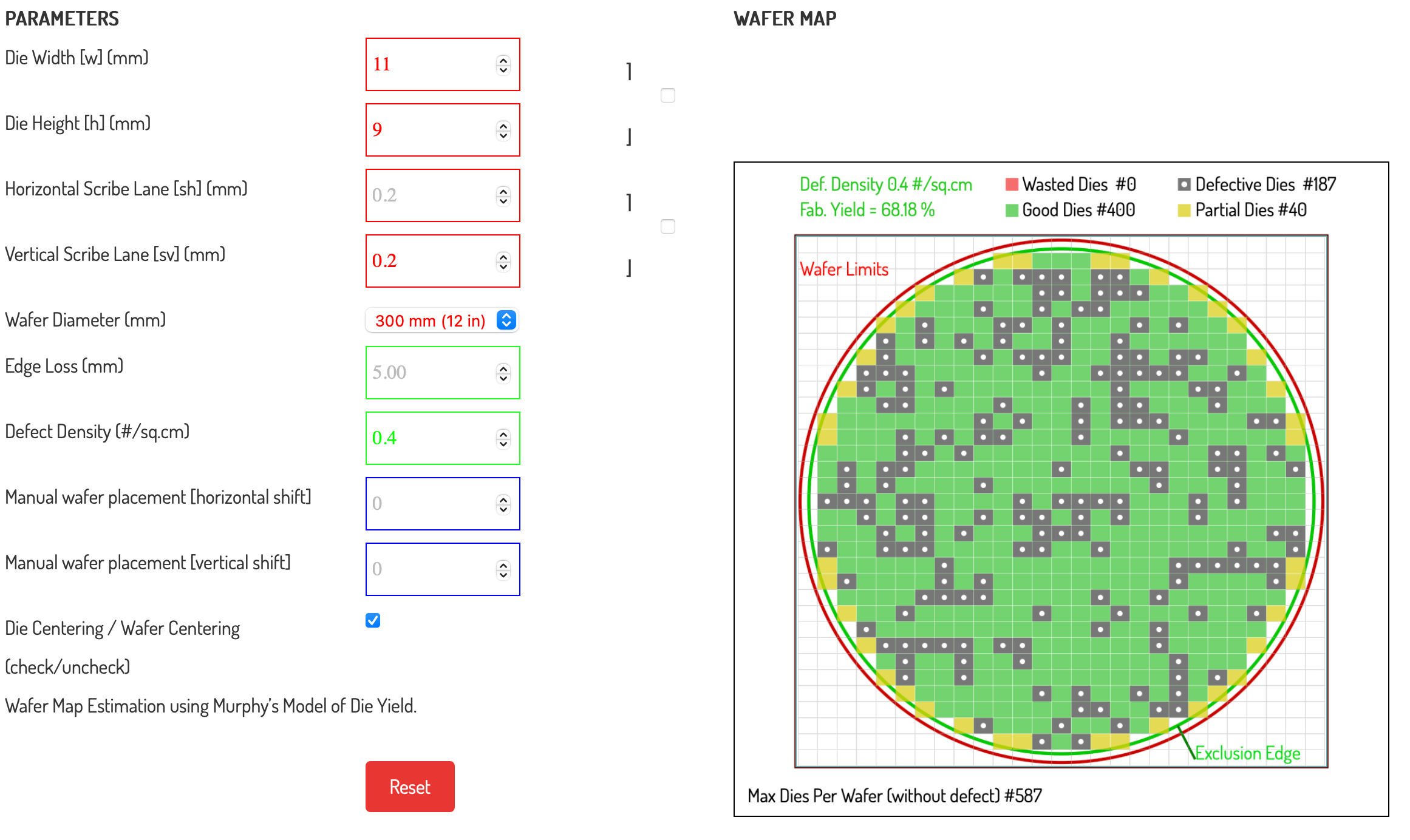

Secondly, not all processors are large. For example, Apple's A18 Pro system-on-chip for iPhone 16 Pro smartphones is 105 mm^2, and this is a very big processor for consumer devices. 105 mm^2 (let's assume it is an 11´9 mm design) gives us 625 die candidates per 300-mm wafer, and at a defect density of 0.4 def/cm^2, it gives us 587 perfectly yielded dies at a 68.2% yield. Again, Apple probably implements loads of redundancies into its designs, so the actual yield of sellable chips is higher.

In general, Intel says its 18A process technology shows promising defect density figures of 0.4 defects per square centimeter for now. While this density is slightly higher than TSMC's benchmarks at comparable stages of development, it is within industry standards for advanced nodes and sufficient for generating usable yields depending on die size and design redundancies. Larger dies, like Broadcom's and Nvidia's AI chiplets, face more significant yield challenges, but advanced redundancy techniques should probably mitigate these issues, enabling a viable number of sellable chips. Meanwhile, smaller processors, such as Apple's A18 Pro, achieve significantly higher yields even at the same defect density.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

why_wolf "While this density is slightly higher than TSMC's benchmarks at comparable stages of development,"Reply

Why is the word "benchmarks" just linked to every Tom's article with the word benchmark in it? Completely pointless. -

jkflipflop98 Yeah that "less than 10% yields" crap that's making the rounds is just that. . . crap. That's not even close to being accurate. Sad that so many news outlets have ran with this garbage.Reply -

Pierce2623 Reply

As we already knew, yields depend on die size more than defect density. Like they mentioned, you’ll only get 9 perfect 5090 dies out of a wafer. Thing is Nvidia disables about 15% of the die for a 4099/5090 so most of “not-perfect” dies will still be good for 4080 super at least. Now they’re even putting 40% deactivated ad102 in 4070ti supers. So obviously those chips weren’t good enough for more expensive GPUs.jkflipflop98 said:Yeah that "less than 10% yields" crap that's making the rounds is just that. . . crap. That's not even close to being accurate. Sad that so many news outlets have ran with this garbage. -

phead128 the interim Co-CEO just two days ago admitted 18A has production snags which will delay production from H1 2025 to H2 2025, presumably this is tape-out (not HVM).Reply

So this is consistent with rumors of poor yields of 18A.

Anyways, Pat wouldn't have been fired is 18A was amazing, that's plainly obvious to anyone with half a brain. -

thestryker Reply

Care to cite a source for this?phead128 said:the interim Co-CEO just two days ago admitted 18A has production snags which will delay production from H1 2025 to H2 2025, presumably this is tape-out (not HVM). -

watzupken I think anyone can try and defend, but if there is no significant takers on Intel’s 18A, it’s a pointless debate. I may not know my stuff here, but potential Intel clients will assess it themselves to see if the foundry is fit for their requirement/ expectations.Reply -

phead128 Reply

Yes, it was interim co-CEO talking during an investor presentation about 4 days ago.thestryker said:Care to cite a source for this?

https://www.investing.com/news/stock-market-news/intel-shares-fall-post-disappointing-investor-update-93CH-3757197

On Thursday, Intel Corporation (NASDAQ:INTC) experienced a decline in share value, dropping over 3% following a lackluster investor presentation held the previous day. The presentation, led by the Chief Financial Officer who has also been named interim co-CEO, failed to instill confidence among investors, according to analysts from Lynx Equity Strategies.

The analysts highlighted that the CFO's affirmation of standing by the previous earnings guidance was not persuasive, casting doubts on whether the company's quarter is on track to meet expectations. Furthermore, the anticipated progress on Intel's 18A node technology seems to have hit a snag, with the production ramp now postponed from the first half of 2025 to the second half.

The lack of clarity regarding external customers for the 18A node, coupled with the absence of concrete plans for the utilization of funds from the CHIPS Act, added to investor concerns. Additionally, the analysts pointed out vague statements about improving margins for Intel Foundry Services (IFS) next year, and a downward revision of product margin outlook, particularly for Lunar Lake, due to a price increase at competitor TSMC.

This is likely referring to 18A tape-out, which Pat said was H1 2025, which is now delayed to H2 2025. This is not likely talking about HVM, which is likely delayed to 2026. It also echos what @watzupken said, there is no major secured customers for 18A nodes, atleast not enough to get an ROI and justify the billions in fab spending. While I am not saying the yields are exactly less than 10%, I can clearly see the interim co-CEO saying 18A is having production delays and issues. -

Pierce2623 Reply

They haven’t even taped out a chip on 18a yet? People on here were claiming Arrow Lake would use 18a. I wasn’t aware they haven’t even reached a single tape out.phead128 said:Yes, it was interim co-CEO talking during an investor presentation about 4 days ago.

https://www.investing.com/news/stock-market-news/intel-shares-fall-post-disappointing-investor-update-93CH-3757197

This is likely referring to 18A tape-out, which Pat said was H1 2025, which is now delayed to H2 2025. This is not likely talking about HVM, which is likely delayed to 2026. It also echos what @watzupken said, there is no major secured customers for 18A nodes, atleast not enough to get an ROI and justify the billions in fab spending. While I am not saying the yields are exactly less than 10%, I can clearly see the interim co-CEO saying 18A is having production delays and issues.